|

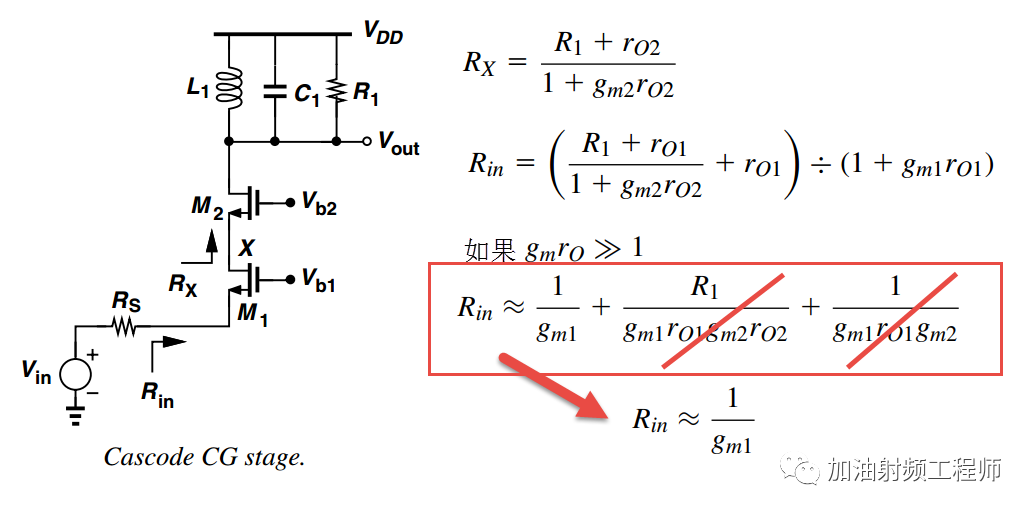

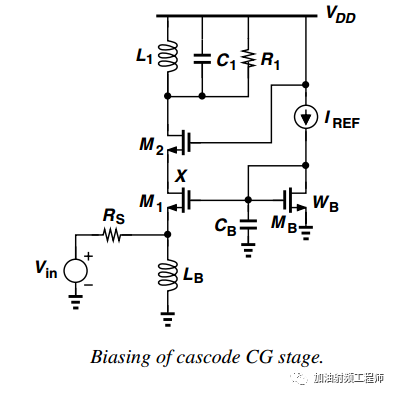

Cascode CG stage是另一种实现低输入阻抗的电路,如下图所示。

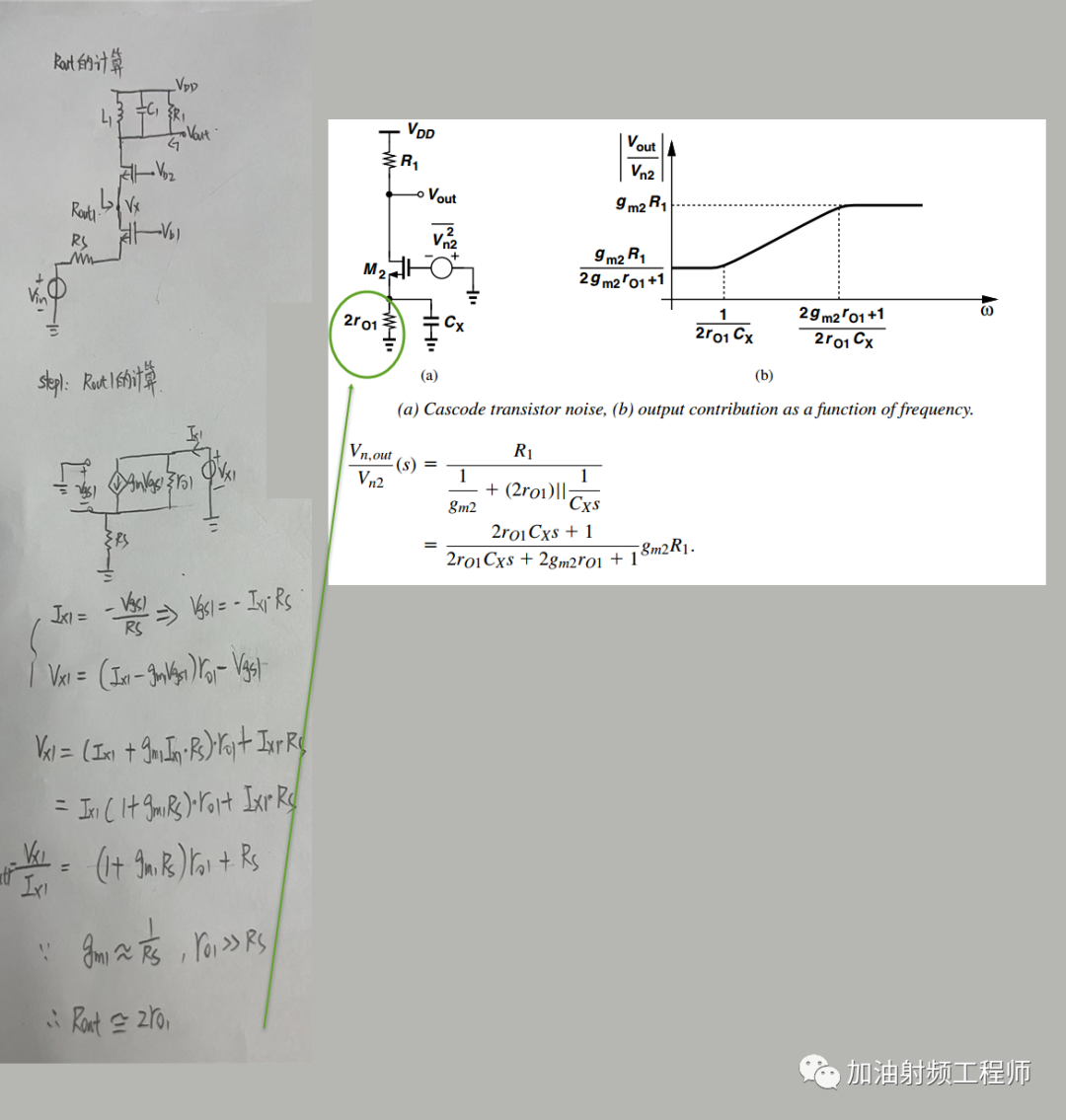

因为增加了一个管子M2,所以很明显的,会带来两个问题: (1) M2带来的噪声贡献 (2) 由于两个器件堆叠,带来的电压余量的减小。 可是为啥,M2会带来问题,但是还要提出Cascode CG stage呢?书中没有讲。 推导了一下,发现Rin,Rout,Av和CG stage都一样,所以这个问题还没想通。应该是在考虑沟道调制效应的时候,会有所优势。这个今天先悬在那,后续再推导一下。 关于上面说的两个问题,razavi的书上做了很详细的说明,总的一句话,就是,在特定条件下,这两个问题都不是问题。 关于第一个问题,结论是,M2带来的噪声贡献与频率相关,当小于某个频点时,带来的噪声可忽略不计。 如下图所示,对上面的Cascode CG stage做一系列简化,包括: (1) 用输出电阻2ro1来替代M1,且CX=CDB1+CGD1+CSB2. (2) 用电阻R1来替代LC tank (3) 忽略VGS2,沟道调制效应,M2的体效应 推导一下,即可以写出M2的热噪声Vn2到输出端的传输函数。

从上图中的传输函数可知,M2的噪声贡献,当频率小于1/(2ro1Cx)时,是可以忽略的,但当大于该频率时,噪声就开始放大了。 因为CX和Cgs相当,且2ro1>>1/gm,我们注意到

也就是说,当零频远低于管子的特征频率fT时,M2对电路噪声的贡献是很小的。 第二个问题是关于电压余量的,即随着工艺的尺寸变小,供电电压也越小,那会不会造成管子供电电压不够,不足以支撑其正常的工作状态。 书中也做了详细的分析,答案是只要选择合适的电压,则不会。

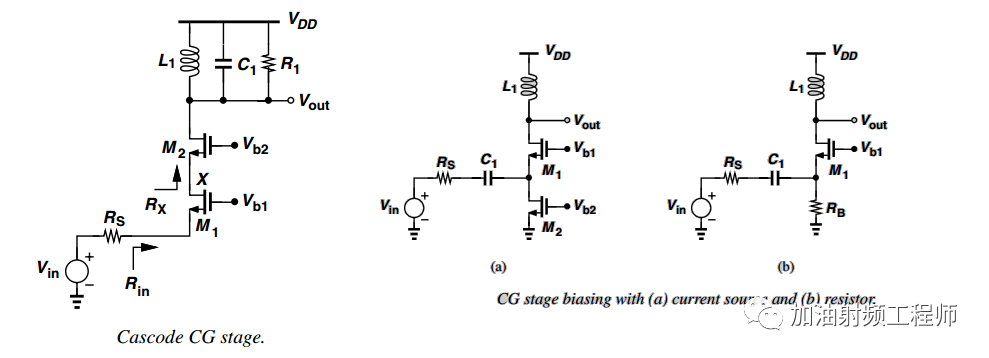

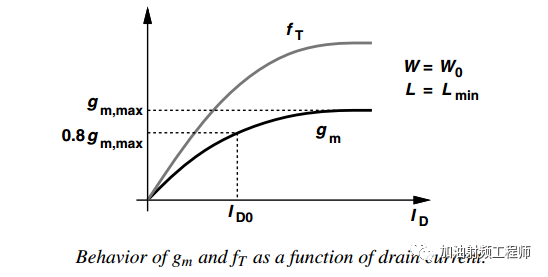

以下是理由,有点绕,但是沉下心来,还是可以看懂的。 其基本原则,就是为了保证管子处于饱和状态,则要求管子的电压满足VGS-VDS 现在开始绕: M2的漏极电压为VDD; 为了保证M2处于饱和状态,则要求Vb2-VDD VX=VDD-VGS2(因为VGS2=Vb2-VX,所以VGS2=VDD-VX); 为了保证M1处于饱和状态,要求VGD1=Vb1-VX 所以M1的源极电压VS1不能超过VDD-VGS2-(VGS1-VTH1)(因为VGS1=Vb1-Vs1,所以Vs1=Vb1-VGS1 所以只要VDD>VGS2+(VGS1-VTH),电路就可以处于合适的偏置状态,即我们可以说,两个管子消耗的电压为VGS2+(VGS1-VTH1)。 至于M1的源极到地的供电路径,这边没有选上右图(a)中的电流源M2,也没有选上右图(b)中的电阻,而是选择了电感。如下图所示。 这样可以避免在噪声和电压余量之间做选择,同时能够抵消电路的输入电容。 在现代RF设计中,LB和L1都集成在芯片上。 书中,给出了该种架构的设计步骤,根据这个步骤,可以得到初始值。 确定工艺后,即可知道供电电压;同时肯定也知道工作频率。 设计分为以下几步: step1: 给M1选择合适的尺寸和偏置电压,gm=1/(50ohm)。 那具体怎么选呢? 晶体管的长度设置为工艺允许的最小长度,主要需要确定的是晶体管的宽度和漏极电流。 使用电路仿真,绘制出NMOS晶体管在给定宽度W0的情况下,跨导和fT与漏极电流的变化关系,如下图所示。 为了避免额外的功耗,选择一个偏置电流ID0,可以提供饱和gmax的80%~90%。 使得宽度和漏极电流处于一个最优的状态。 W0和ID0知道后,其他跨导值,可以通过简单对这两个值成比例的放大或者缩小得到。 在获得1/gm1=50 ohm时,根据其对应的尺寸和偏置电流,进而得到overdrive电压。 从这些措施来看,好像gmID曲线的方法也适用。 |