|

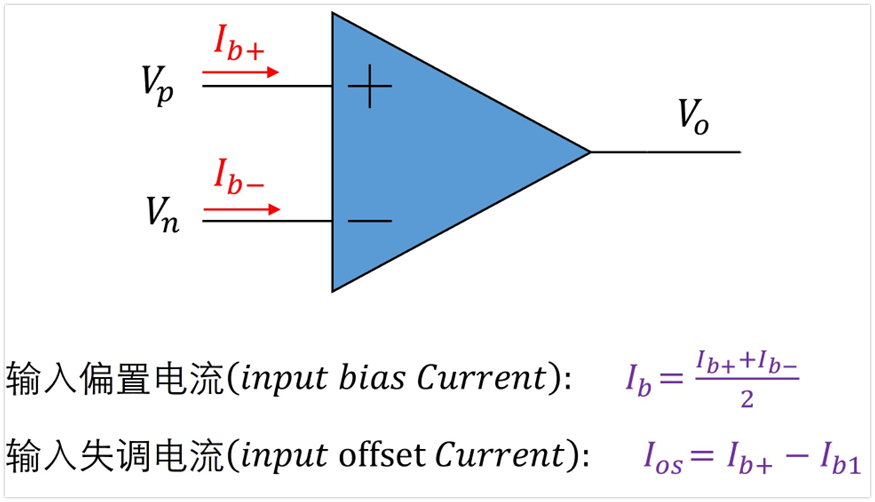

今天来说一说运放的偏置电流和失调电流,我们还是带着问题看,先想想下面几个问题: 1、为什么不同运放的偏置电流差这么多?原因是什么? 2、运放输入端偏置电流方向是什么样的呢?是可以流进,也可以流出的吗? 3、实际应用中偏置电流是如何引起误差的呢? 4、实际应用中失调电流是如何引起误差的呢? 5、电路设计时应该如何考虑偏置电流和失调电流的影响呢? 要想回答上面这些问题,我们首先需要了解偏置电流和失调电流到底是怎么产生的。 偏置电流、失调电流是什么 我们前面说过,理想运放的同相端和反相端的输入电流为0,所以才有“虚断”的说法,但是实际运放的输入管脚都会流入或流出少量的电流,并且经常同相端的电流和反相端的电流还不相等。 我们如果将流入同相端的电流用Ib+表示,流入反相端的电流用Ib-表示,那么放大器的输入偏置电流Ib就是Ib+和Ib-的平均值,即Ib=(Ib+ + Ib-)/2。

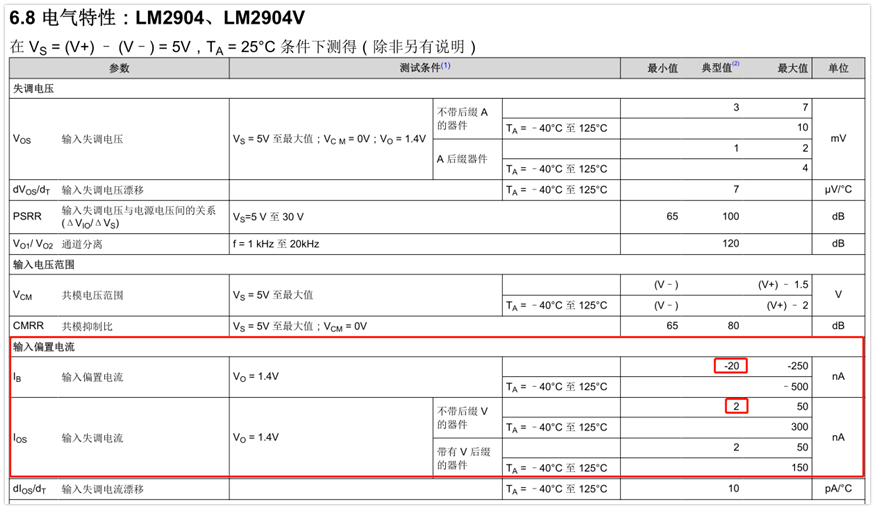

可以看到,偏置电流就是同相和反相端电流的平均值,而失调电流,衡量的是2相电流之间的差异。 我们还是以前几期的LM2904举例子,如下图:

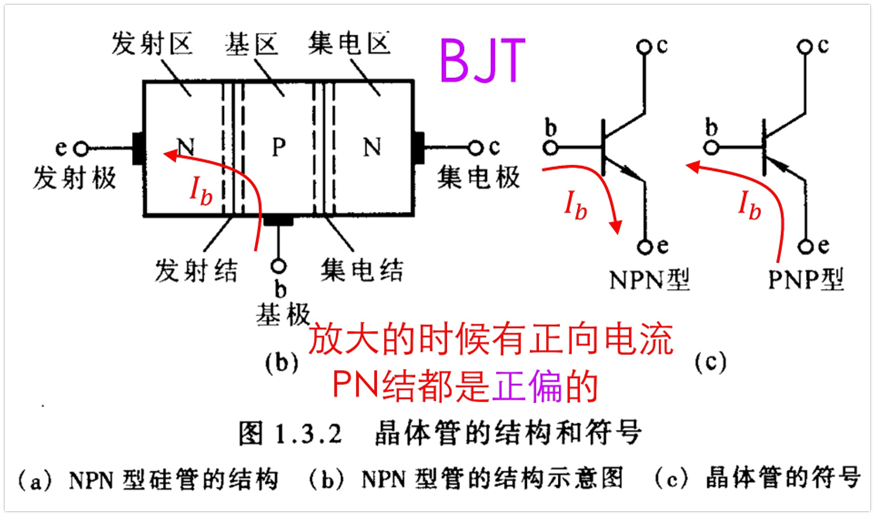

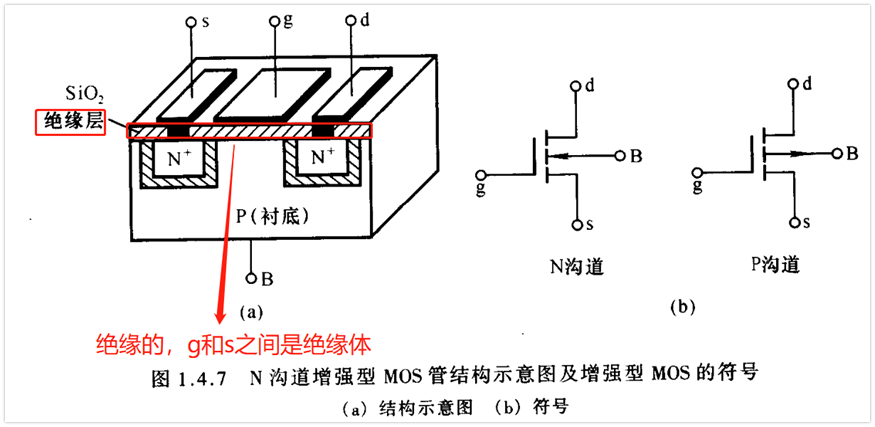

图中标注IB就是LM2904的输入偏置电流,典型值为-20nA,Ios为输入失调电流,典型值为2nA。失调电流是偏置电流的十分之一,说明这个放大器同相端和反相端的电流还是比较接近的。 那么偏置电流是如何产生的呢? 偏置电流的来源 显然,偏置电流取决于流入或流出放大器同相端和反相端电流的大小,这自然和放大器输入级的构造晶体管类型有莫大的关系。 我们知道,晶体管有好几种,比如双极性晶体管BJT,结型场效应晶体管(JFET)和金属氧化物半导体场效应晶体管(MOSFET)。然后它们又分什么NPN,PNP,N沟通,P沟道,这样算起来种类还是不少的。 就输入阻抗而言,一般是MOSFET>JFET>BJT的,我是怎么记住这个的呢?我没有刻意去记住,而是理解的方式,脑子里面回想下这几个管子的结构也就出来了,这里也分享一下。 大体是这样的: BJT三极管我们应该都比较熟,其是电流驱动的,其放大的时候,要给它合适偏置,b和e之间是有正向电压的,是一个有正向压降的PN结,处于放大区的时候里面是有电流流动的。

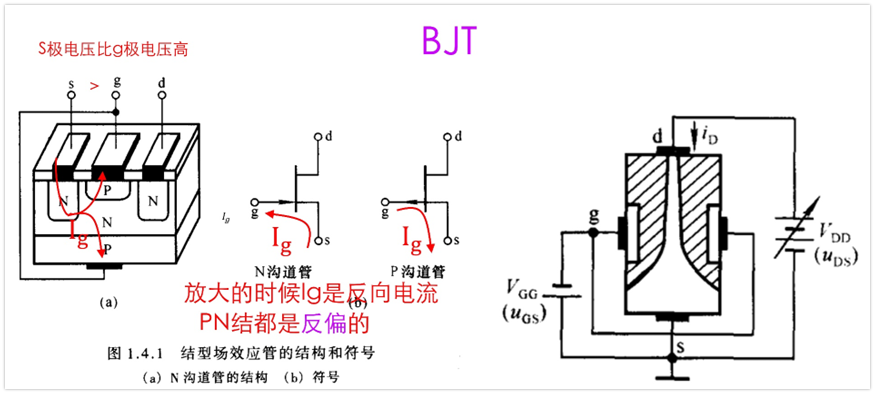

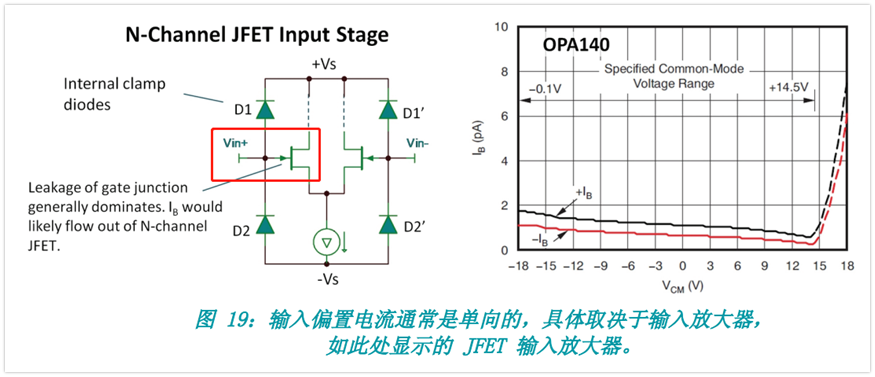

JFET分立管子用得非常少,我到目前还没用过这个,但是教材上都有这个器件的结构,集成运放也是有这种结构的,其工作的时候,输入端也可以理解为一个PN结,不过是反偏的(通过反偏控制耗尽区的厚度来控制导电沟道的宽度),也就是说电流很小。但是我们知道施加反向电压的PN结也是会漏电的,就像我们用的二极管,也会有漏电流这个参数。显然,这个电流要一般比三极管的输入电流Ibe要小,那么其直流输入阻抗也就比其要小。

MOSFET我们用得比较多,其栅极与衬底极是二氧化硅绝缘体,既然称为绝缘体,那阻抗就是非常大了,基本没有电流,因此,它的直流输入阻抗是最高的。

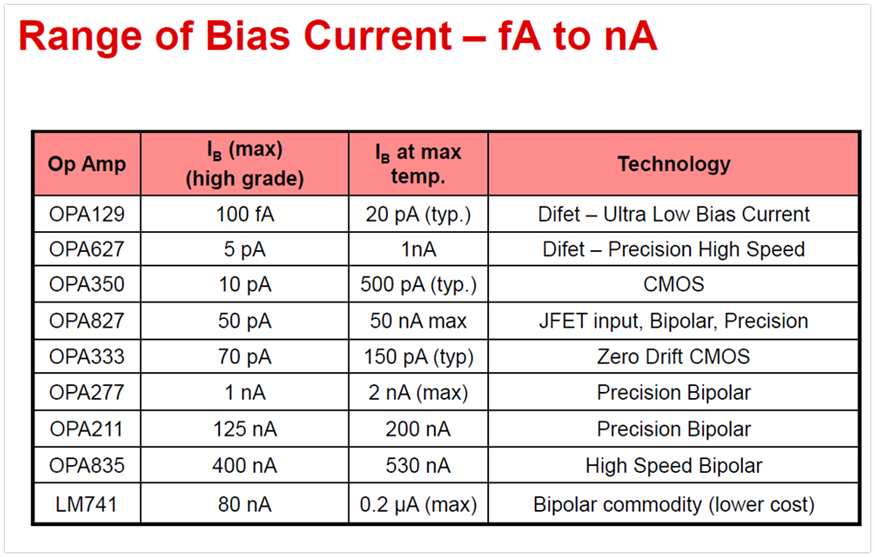

大概总结下:BJT放大时输入端是正向的PN结,电流较大;JFET放大时输入端是反向的PN结,电流主要是漏电流,很小;CMOS放大时输入端是绝缘的,直流电流最小。 扯得有点远,其实说这个主要是因为我在网上看到几款放大器芯片的偏置电流表格,它们之间差异是很大的,如下表:

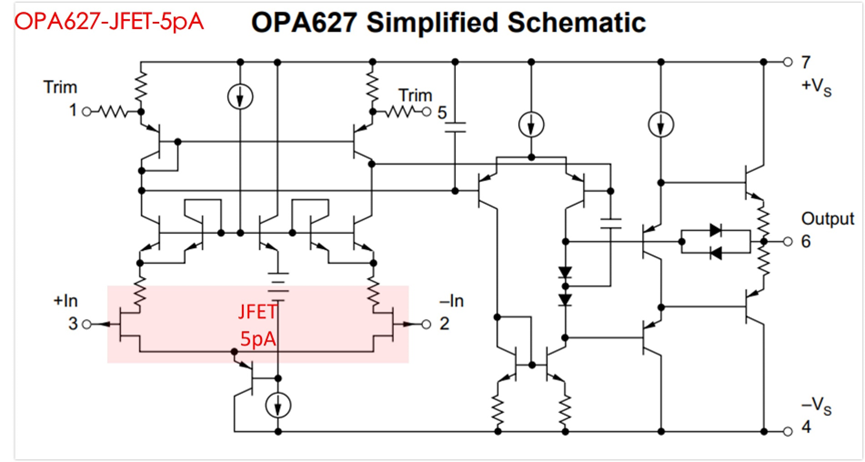

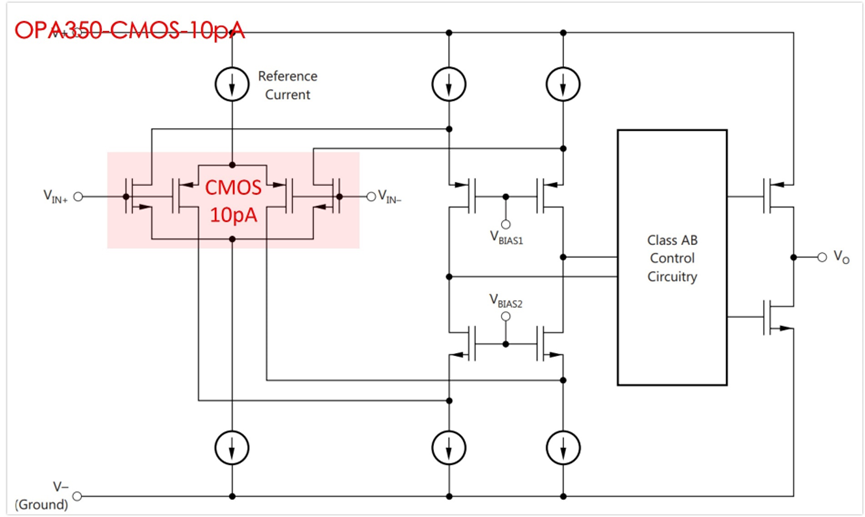

可以看到,不同放大器直接的偏置电流差异很大,从pA到nA级别,成千上万倍的差异。 翻了下上面这几个放大器的手册,挑了3个没特殊处理偏置电流的放大器,看了看OPA627,OPA350,OPA211等 3个放大器的输入级,如下图: OPA627-JFET-5pA:

OPA350-CMOS-10pA:

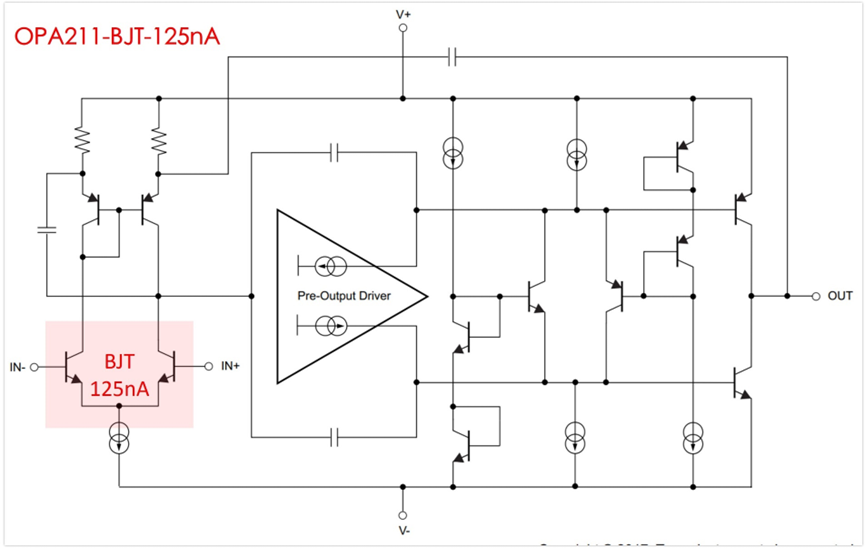

OPA211-BJT-125nA:

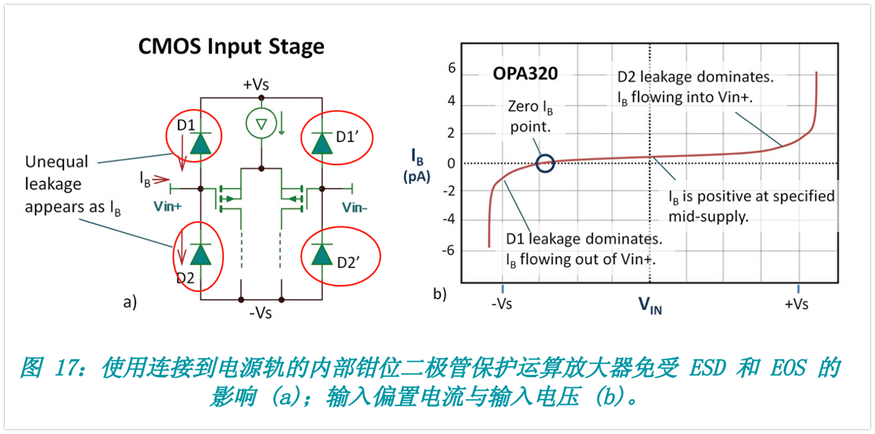

结合前面的表格,大致可以看出2点: 1、Bipolar结构的偏置电流Ib是最高的, nA级别;而JFET和CMOS差不多,都是pA级别的(有特殊处理的除外)。 2、JFET和CMOS的温漂非常严重,温度最高值相对于典型值有几百倍甚至上千倍,也就是温漂非常高(OPA129,OPA333专门处理过的除外),而BJT(Bipolar)温漂相对较小,最高温度时相对典型值也就2-3倍左右。 结合前面的表格,这里不禁有两个疑问: 1、前面不说CMOS的输入阻抗要比JFET的阻抗要高吗?为啥偏置电流差不多呢? 2、为啥CMOS和JFET结构的偏置电流温漂达到几百上千倍,而BJT(Bipolar)结构的偏置电流温漂只有2-3倍? 这两个问题可以在TI的文档《有关运算放大器设计主题的博客文章汇编》里面的第8节和第9节找到答案。 文档下载链接是这个: https://www.ti.com.cn/cn/lit/eb/zhct321/zhct321.pdf?ts=1676037417171 意思大致如下: 因为CMOS和JFET的输入阻抗太高了,导致很容易受到静电导致击穿损坏,所以一般都会加上ESD管。 如下图的CMOS输入结构。因为CMOS本身栅极是绝缘的,说流入电流基本为0没问题,即阻抗特别特别高。但是因为ESD保护加了保护二极管子D1和D2,正常情况下,它俩都是反偏的,那么就有反向漏电流,这个电流自然比CMOS本身栅极绝缘体的电流要高,因此,实际CMOS的偏置电流就由这两个管子的差值决定。

这其实也就解释了上面的第一个问题——为什么CMOS和JFET结构的放大器,偏置电流量级是差不多的?因为它们的偏置电流都是反偏PN结的漏电流形成的。 除此之外,我们还可以看到下面这些: 根据基尔霍夫电流定律,输入节点电流和为0,我们忽略CMOS栅极绝缘体(gs之间)基本为0的电流,那么流进放大器的电流就是下管电流减去上管电流。 并且容易想到,如果Vin输入电压靠近正电源轨道+Vs,那么上管D1的反向电压就比较小,而D2的反向电压就比较大,如果D1和D2的工艺完全一样,比如D1的漏电电流要小于D2的漏电流,那么自然IB就是流进放大器的,即IB为正值。 反之,如果Vin的输入电压靠近负电源轨-Vs,那么D1的电压就要大于D2电压,D1的电流也就大于D2的电流,那么IB就是流出放大器,即IB为负值。 因此我们最终看到右边的曲线,IB在靠近-Vs时是负的,而靠近+Vs时是正的。这说明什么呢?说明了,这个放大器的偏置电流的方向,还跟输入端的共模电压有关系。 我们再看JFET的输入极 前面JFET的结构我们已经知道了,N沟通的JFET处于放大的时候,输入级电流是往外流的,当然,D1和D2依然有漏电流。 但是TI文档《有关运算放大器设计主题的博客文章汇编》里面指出:输入晶体管的栅极是一个二极管结,它的泄漏电流通常为输入偏置电流的主导来源。输入栅极结通常更大,因此泄漏电流也比保护二极管更大。因此,输入偏置电流更多的时候是单向的。它可能会发生变化,具体取决于放大器。 所以JFET输入级的偏置电流是单向的,是往外流的。

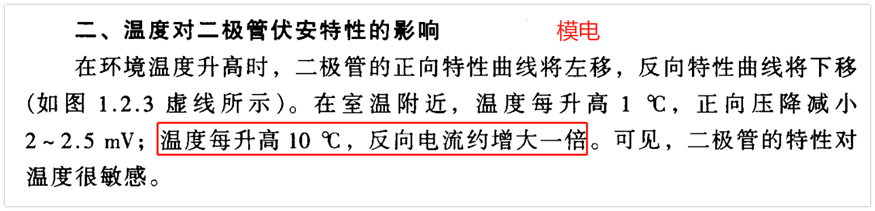

这里发觉得好像有一个错误,因为上图中OPA140曲线中的IB都是正值,按理说往运放外部流应该是负值,上图中左边的英文解释(Ib would likely flow of N-channel JFET)也说明了这个电流是往外的。 温漂的问题 至于前面提到的为什么CMOS和JFET输入级的偏置电流温漂这么大,到这里应该就是显然的问题了,因为它俩产生的原因都是PN结的反向漏电流。

这玩意跟二极管的反向漏电流的温漂一样:温度每升高10℃,漏电流增加1倍,典型值一般是25℃时候的,温度升高到125℃,那么就有10个10℃,增加的倍数就是2^10=1024,这可不就上千倍了嘛。 bipolar结构的温漂为什么这么小呢?大概只有2~3倍左右的样子,这个也比较容易看出来。以前面的OPA211为例子。

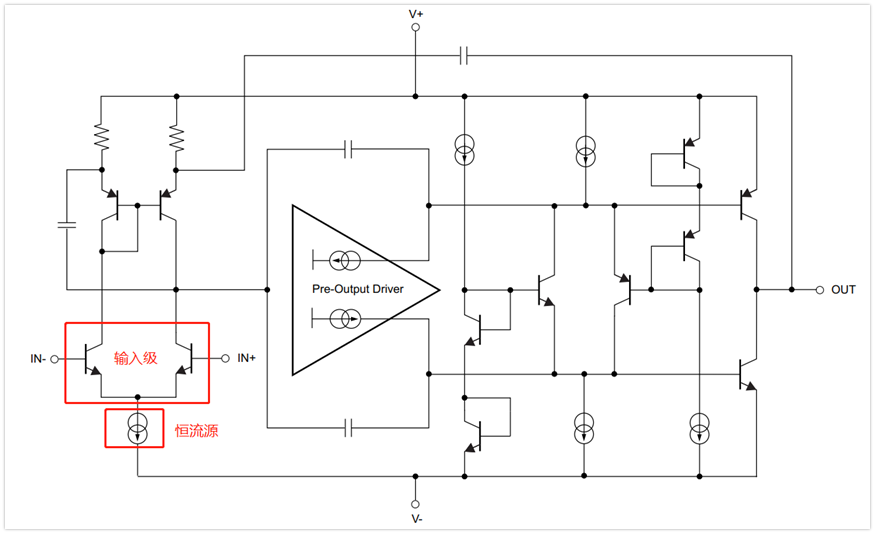

可以看到,输入级底下是个恒流源,虽然它也是晶体管构成的,有温漂,但肯定不会发生数量级的变化,那么输入级的两个晶体管的Ic电流也就不会飘得太多,最终输入偏置电流IB也就不会飘得太多。 输入失调电流 说完了偏置电流,失调电流就简单了。同失调电压产生的原因相同,半导体工艺难以做到输入两个晶体管的完全匹配,导致流入输入级晶体管的电流有差别,因此也就有了失调电流。

推荐一本正在看的书——《运算放大器参数解析与LTspice应用仿真》,还不错,运放的各种参数讲得挺明白,还有实例。 小结 本期主要说了下运放输入偏置电流是咋形成的,没想到写的还挺长,因为我也是边写边查边想,发现不知道的也就再去查查看看。至于开篇提到的5个问题,这篇内容也就只能回答2个,剩下的3个留着下次吧。 小结如下: 1、不同运放的偏置电流差异很大,是因为其输入级的构造不同,简单说就是它是用的BJT,还是JFET,还是CMOS。其中BJT的偏置电流最大,在nA级别,JFET和CMOS差不多,在pA级别(有专门的处理的除外)。 2、BJT结构的偏置电流温漂较小,而JFET和CMOS因为其偏置电流都是由PN结反向漏电流形成的,因此温漂较大。 3、不同运放偏置电流的反向特性是不一样的,有的都是向里,有的是向外,也有跟共模电压有关系的,能里能外。 常看我文章的兄弟们应该知道,我一向是写我是怎么想的,怎么查的,并不直接摆结论,很多观点其实是结合我自身的知识体系,作出的一些延展,个人理解,目前来说,我自认为它们都是正确的,因为可以融入到我的知识体系。 所以呢,错误是难免的,如果兄弟们发现有啥问题,请留言指出来。 审核编辑:汤梓红 (责任编辑:admin) |