|

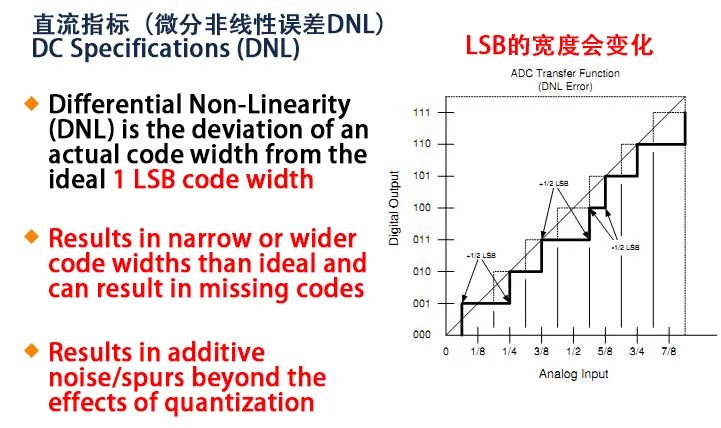

众所周知,ADC主要用于对模拟信号进行数字采集,以进行数据处理。 我们周围的信号一般都是不断变化的模拟量,如光、温度、速度、压力、声音等。 然而,我们大多数人都使用数字设备。 如果我们想方便地使用和处理信息,就需要将模拟量转换为数字量,并传送到微控制器或微处理器。 那么ADC转换是如何实现的呢? 这是一个什么样的过程? 阅读下面的笔记,你一定会对模数转换器有更全面、更系统的了解。 各位同行们,大家好啊,今天又来给大家分享ADC方面的学习笔记啦,听闻上一篇笔记大家都挺满意呢,那么这一次还是希望大家喜欢哦。 一、ADC的参数 1、分辨率 就是最小能够分辨的模拟电压值,例如12位ADC,Vref为3.3V最小分辨率即:Vref/2的12次方=0.8mv。 2、转换速度 即每秒转换的数字量,例如100kSPS,也常表示为每个数字量的转换时间如15us 3、输出接口 有串行或者并行接口 4、工作电压,基准电压(内部或者外部基准),封装。 5、DNL 微分非线性误差

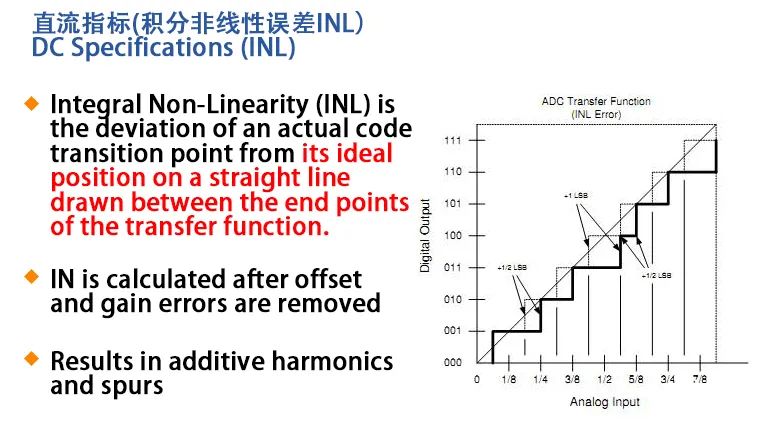

6、INL积分非线性误差

这两种误差具有一定随机性,因此ADC会出现误码。 7、几种重要的交流参数

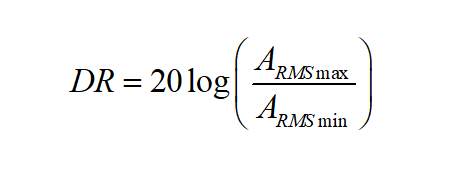

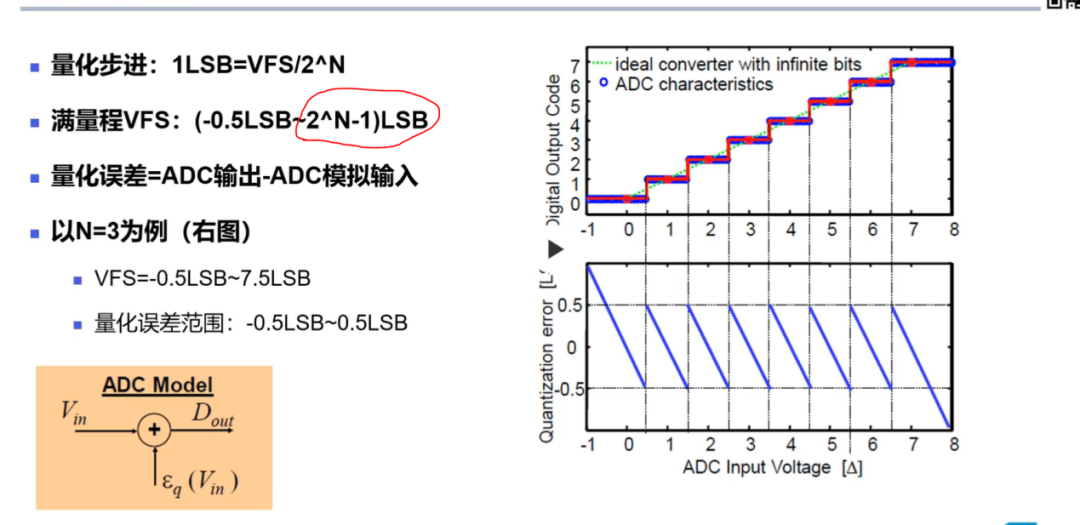

二、信噪失真比与有效位数 (ENOB) 采样是利用模拟开关将连续变化的模拟量变成离散的数字量,由于经采样后形成的数字量宽度较窄,经过保持电路可将窄脉冲展宽,形成梯形波。 量化是将阶梯形模拟信号中各个电压值转化为某个最小单位的整数倍,便于用数字量来表示。 编码是将量化的结果(即整数倍值)用二进制数码来表示。 这个过程则实现了模数转换。 分辨率与动态范围 N, DR ADC分辨率为用于表示模拟输入信号的位数。 为了更准确地复现模拟信号,须提高分辨率,使用较高分辨率的ADC也降低了量化误差。 但成本就上去了。 动态范围(DR)定义为器件本底噪声至其规定最大输出电平之间的范围,通常用dB表示。 ADC的动态范围是指ADC能够分辨的信号幅值范围; ADC的分辨率位数(N)决定ADC的动态范围,代表ADC可测量的输入信号等级范围,DR可定义为:

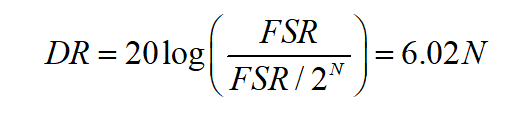

由于信号在给定时间视窗内的RMS幅值取决于信号幅值在该时间视窗内如何变化,因此ADC的DR变化取决于输入信号特征。 对于其满量程范围(FSR)内的恒定DC输入而言,理想的N位ADC可分别测量FSR和FSR/2N的最大及最小RMS幅值。 因此,ADC的DR为:

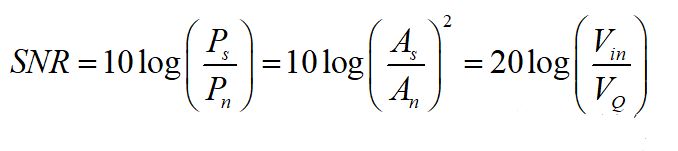

对于正弦波信号输入而言,正弦波输入信号的最小可测量RMS幅值受量化误差的限制,正弦波输入信号的理想ADC的DR是: DR=6.02N+1.76dB 假设ADC的动态范围为60dB,则其可分辨的信号幅值为x至1000x。 通常动态范围非常重要,因为如果信号太大,则会造成ADC输入过量程; 如果信号太小,则会被淹没在转换器的量化噪声中。 信噪比与信噪失真比 信噪比, 信噪比 数模转换器的信噪比(SNR)是指输入信号功率与噪声功率的比值,这里用来量化数据转换器内的噪声,SNR也能使用信号幅度和噪声幅度的RMS值来衡量,以dB为单位。

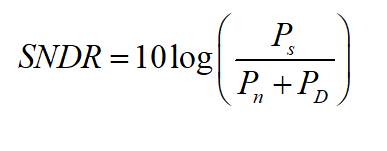

在满刻度正弦波输入的条件下,ADC的理论最高SNR从量化噪声推导而得,表达式为: 信噪比=6.02N+1.76dB 这里N是理想ADC的位数,对于理想的N位数据转换器(不考虑谐波失真)的正弦波输入,整个奈奎斯特带宽上能达到的最佳SNR。 但对于实际的ADC,除了量化噪声,数据转换器的SNR也会受到自身热噪声和采样时钟相位噪声的限制。 噪声来自主要有三个源头: • 量化噪声 • ADC热噪声 • 抖动或采样不确定噪声 信号与噪声失真比(Signal to Noise And Distortion,SINAD)指输入正弦波时,RMS信号功率与总噪声功率和输出端(不含DC)的所有其他频率分量功率加上所有其他谐波分量功率的RMS和的比值。 SNDR是用于衡量数据转换器的动态性能的关键参数之一,它包含奈奎斯特带宽上的所有噪声和杂散。 SNDR的表达式为:

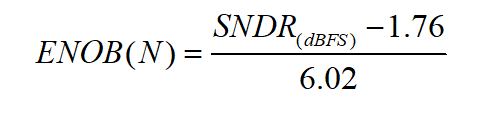

其中,信号功率是有用信号、噪声和失真分量的平均功率。 SNDR的单位是分贝(dB),SNDR将所有不良频率分量与输入频率做比较,反映的是输入信号的质量,从总体上衡量数据转换器的动态性能。 SNDR越大,输入功率中的噪声和杂散比率越小。 有效位数 伊诺布 有效位数 (ENOB) 是用于衡量数据转换器相对于输入信号在奈奎斯特带宽上的转换质量(以位为单位)的参数。 这里的ENOB假定转换器是拥有理论上完美性能,不发生失真,唯一产生的噪声是量化噪声,所以SNR 等于SNDR,即SNR(dBFS)= 6.02N+1.76dB。 因此,ENOB也是SNDR的另一种表达方式:

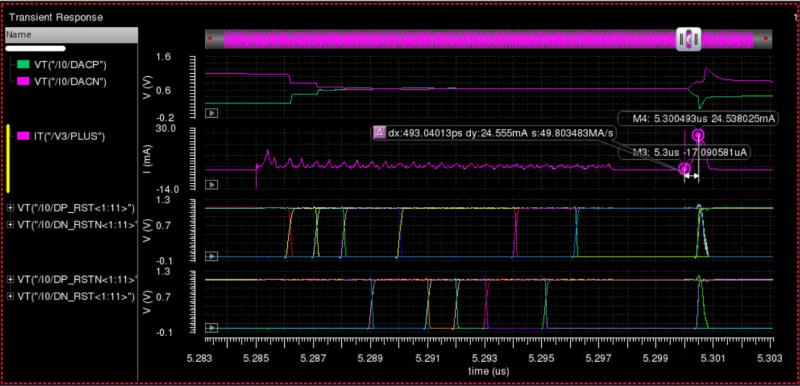

然而,对于非理想数据转换器而言,SNDR和ENOB会发生劣化,包含噪声和其他缺陷,例如器件热噪声、输出代码缺失、谐波、AC/DC非线性、增益/偏移误差和孔径时钟相噪或抖动。 外部偏置基准源和电源轨上的噪声也会降低ENOB。 总谐波失真(THD)测量信号的失真成分,用相对于基波的分贝(dB)表示。 对于ADC,总谐波失真(THD)是所选输入信号谐波的RMS之和与基波之比。 测量时,只有在奈奎斯特限值之内的谐波被包含在内。 类似于THD因非线性原因随输入频率增加而劣化,ENOB值也会随频率加大而劣化。 ENOB来自于SNDR,而SNDR又与THD以及SNR相关联。 要了解数据转换器的准确ENOB,需阅读数据手册中的详细规格和规定的条件。 实际中的ENOB 大部分模拟数据转换器IC厂商一般倾向于推广理想条件下的ENOB,尤其是数据手册标题所载的ENOB值。 然而,大量系统工程师和采购经理仍然好奇的是,为什么测量出的ENOB值和数据手册所载的理想值不同? 实际使用中,由于ADC自身存在噪声和误差,其输出不仅有量化噪声,还有失真引起的高次谐波,因此从未能达到这一SNR值。 计算ADC的有效N:ENOB=(SNR–1.76)/6.02 dB。 假设器件是一款12位ADC,ENOB可能仅为10bit。 但需要注意的是这并不表示把ADC的后两位删掉就可以当成一个理想的10bit ADC来使用,这里ENOB的意思是12bit非理想ADC的SNDR与理想的10bit ADC的SNR相等。 有关ENOB的一些理解要点: • 一般数据转换器数据手册标题显示的“位数”(12位或14位)指的是数字位或电压分辨率。 这与ENOB无关。 • ENOB主要与噪声、非线性和输入频率存在函数关系。 • ENOB会因多种外部不确定性因素(例如时钟源、电源等)而劣化。 • ENOB是在整个奈奎斯特带宽上(DC到fs/2)计算的。 知识点理解:无杂散动态范围(SFDR) 大家在学习ADC的过程中一定有很多问题,我这边也总结了一些学习中遇到的问题,现在分享给大家,希望能从中学习到一些有用的知识。 第一季度 对于ADC的参考电压的rms噪声要求是什么,是小于一个LSB就可以,还是跑train参考电压noise vpp值小于一个LSB? 关于ADC的VREF的噪声(或者波动),首先要区分是低频还是高频。 你们可以去看TI或者ADI的某些高精度(16Bit)ADC,VREF的温度系数其实并不好,在全温度范围内VREF的偏差可能已经几十个LSB了,这是为什么呢? 温度对VREF的影响可以认为是一个低频的噪声源。 对于一个哪怕只有1MSPS的ADC,1s的时间,ADC将会处理100万个数据。 “只要我的速度够快,水晶的伤害就追不上我”。 对于高频的噪声,芯片内部很容易处理,滤波即可。 相较于噪声,我们其实更加关注VREF的有限驱动能力,不管是片内BUFFER,还是外接VREF(封装电感),VREF的有限驱动能力带来的建立误差的影响远远>VREF上噪声的影响。 事实上,冗余的引入就是为了处理VREF以及CDAC网络的有限建立精度问题的。 冗余和CDAC的开关序列(能耗)、CDAC阵列的具体情况(哪一步或者哪几步需要的电荷较多)、比较器的转换时间、VREF的驱动能力都息息相关,这些因素参杂在一起,相互制约 包括PVT Corner,不同的PVT下比较器的时间差异也很大,FF Corner下比较器的速度可能是SS Corner下的50%都不到,比较器越快,对VREF的建立要求越高。 所以从VREF建立的角度,FF可能反而是最差PVT。 第 2 季度 异步的sar,说起来那么多好处,功耗低,速度快,面积也小。 那么pipeline还有什么竞争力呢? 那么同步sar的ADC目前在行业应用中又有什么前景呢? >10bit的几十M,几百M的应用。 功耗面积肯定大很多。 高速SAR成熟以后,即便pipeline,最好也要pipeline-SAR吧高速SAR吃的是工艺进步的红利,蚕食的是pipeline的部分应用领域。 第三季度 采样开始,电容复位时,0.5ns内电源会被抽取25mA电流,采用内置LDO供电感觉有点困难吧,瞬态响应有点快。 对电源供电这块是怎么考虑的呢?

不要光看毛刺电流,要看25mA毛刺电流持续的时间,或者说是电荷Q=I*t,这个电荷如果用一个电容C来提供,带来的压降是deltaV是多少. 电源地上加点decouple电容就行了,当然,电源上的ripple不可避免。 第 4 季度

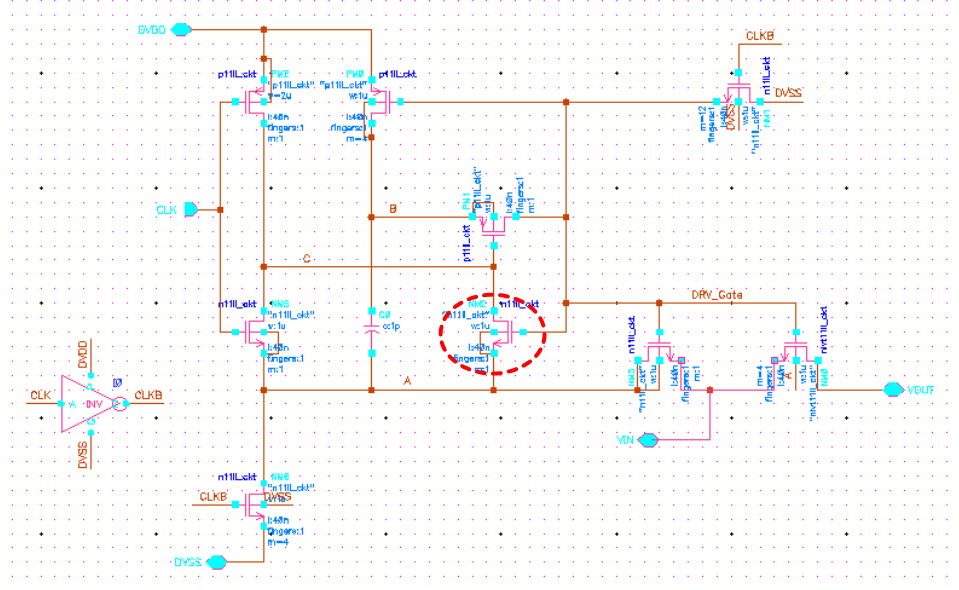

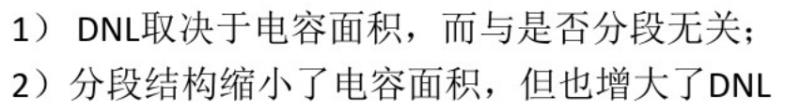

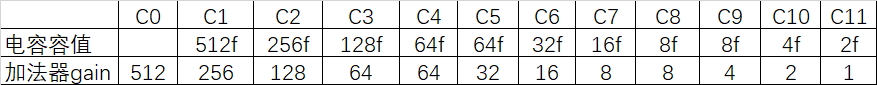

总感觉上图红圈中的器件没啥用,对吗? 这个管子的作用是当A点电位升高导致时NM5关断时,能够继续给PM1提供导通电位。 我按照做好的电路搭了一个自己工艺的,感觉好像就可以工作了,我没有使用带DNW的工艺来做采样开关,感觉也还行,我用的是0.18-5V的工艺,因为我主要是为了MCU的一个模块用,不需要很高的速度,这个电路就跟老师说的,实在太小了,而且很多数字的电路,直接调数字单元库也可以用。 问5a 分段电容结构到底是改善了INL DNL还是恶化了,怎么对整个电容阵列进行建模? 分段并不会改善也不会恶化INL和DNL,前提是采样电容不变的情况下,因为瓶颈在MSB上,分段本身不改变MSB的值,至于整个CDAC建模,把每个电容带上随机失配就可以了。 问5b 单位电容一定的情况下,分断结构,降低了MSB总电容的个数,那么MSB电容总的偏差减小,按DNL INL提升了,这说法有问题吗? 这个结论反了,如果单位电容一定的情况下,分段见笑了MSB电容个数,也就是减小了MSB电容的值,MSB的相对偏差变大,DNL和INL恶化,一般情况下,我们比较两种情况下的DNL,需要基于一个前提,那就是MSB电容值不变。 有这个前提的话,DNL和分段不分段无关。

问6 2级latch相对于里维斯. 格雷增强型在原理上的优势吗? THD 直接可以观察vout-vin的差值,这个差值越小,说明THD越好,差值的分析和锁相环里面的phase noise很像。 输入的导数很大时候,峰值很大,过零点一般最差。 电路中的AC开环曲线去需要和零极点仿真对应。 我举例子了。 CMRR主要从匹配的角度出发去理解。 CMRR=| Adm|/| Acm| PSRR的是说,如果一个opamp是millier,cascode补偿的形式,power 带来的noise会直接在 VGS两端bouncing。 然后穿过频率补偿电容导致恶化。 所以优化的方向时尽量避免这类补偿的方式。 问7

加法器每位的gain是不是有问题? 还是说理解错了? A点电位升高,导致NM5关断了,如果没有这个管子,PM1的gate也就不再升高了,岂不是PM1更容易导通? 反而有了这个管子,导致PM1的gate始终随着A点的升高也在不停的升高,反而不利于PM1的导通呢。 加法器增益和电容值要一一对应,统一大2倍和小2倍对仿真ENOB好像没有影响,不知道对测试有没有影响。 C4对应32,C8对应4。 NM5关断后,PM1的gate主要靠NM1下拉。 如果没有NM1,则PM1的gate为不定态,不一定为低。 A点电压够高,NM5才会关断,B点电压为(A点电压加上一个VDD),如果没有那个NMOS器件,PM1的gate确实是一个高阻点,这个高阻点电压再高应该不会超过VDD(分压原理)),因此把(A点电压加上一个VDD)这个电压传过去,应该是没有问题的。 电容一但充电到vdd,只要pm1使nm2形成自举结构,nm5即使关掉也不影响了。

但是电容充电后,还是要靠nm5的打开pm1的第一次。 B点为高阻点,PM1导通不彻底,DRV_gate电压不等于vin+ VDD,没有实现输入电压自举的目的,你可以看看NM0的栅源电压,应该没有维持恒定的VDD。 如果c电点位如果有高阻状态,那么这个点首先容易被干扰,同时这个点会有几种状态的过度,对我觉得这样会让pm1的导通电阻变化,这会影响drv_gate的控制速度。 等于给自举开关引入非线性。

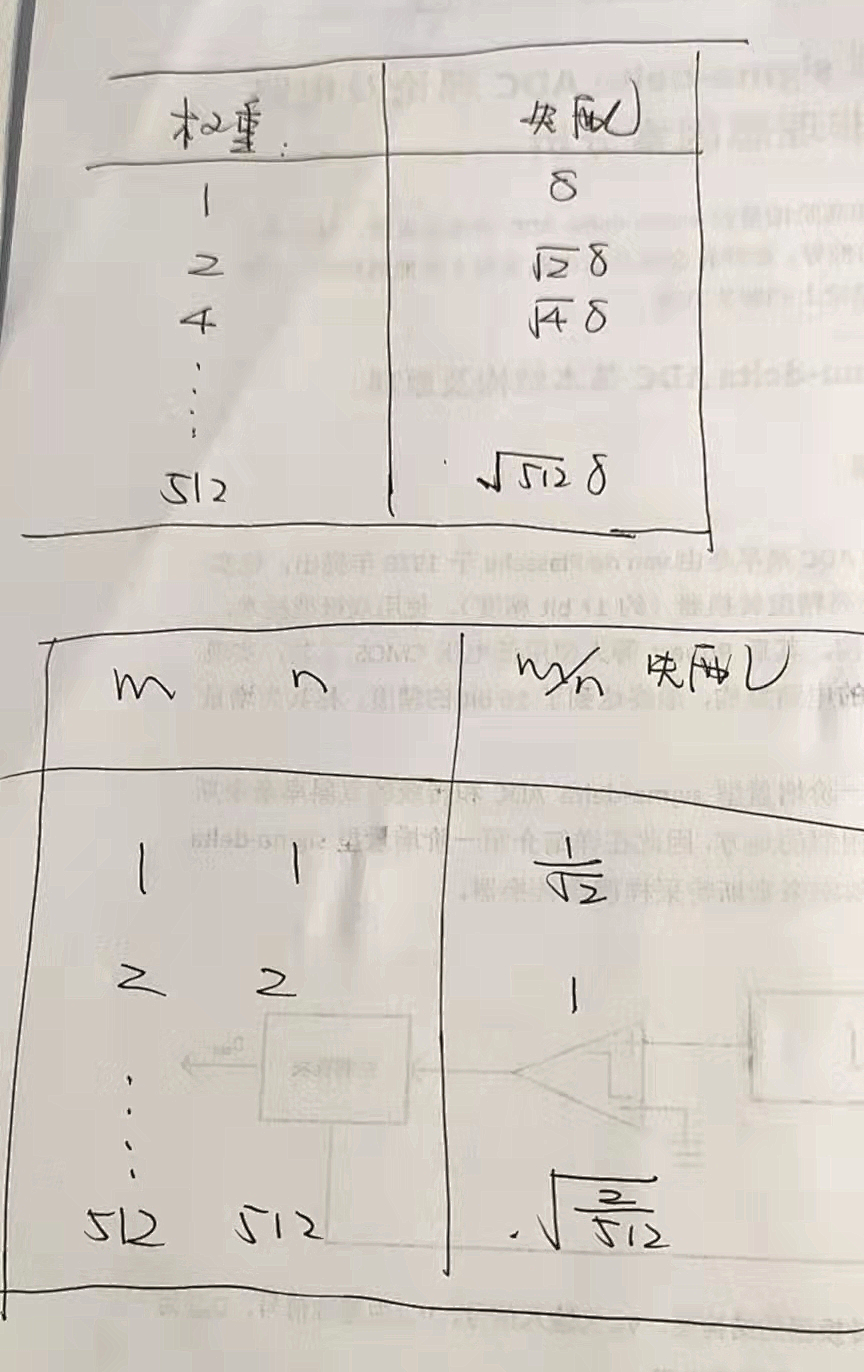

电容越大适配越大,但是这个比例会不一样啊,就是电容每增大两倍变成原来两倍的时候,适配变为原来的跟二倍电容乘以四的时候就融资啊,其实面积也是乘四,这个时候呢,我们的适配会变成两倍。 假设现在十个电容C1是512C2256,然后C1011,我们先做这个假设,那C1在CDC切换的时候,他做的动作是什么呢? 是C的下级板哪一个节约信号,那这个时候上级版的就等效为C1的512和剩余的512去做比,也就这个时候呢,M等于512 N也等于512两个之间去比,然后这个出来的这个值啊,就说我们这个DC的输出,其实就什么这两个的比,其实就是M和N的这个相对配了,这个值是多少呢? 应该是根号,就是开方里面是多少,1/512加1/512,是这么一个值。 但是大家要记得就说我们出来的这个十位的扣的啊,第十位就最高位,最高位其实跟什么合时宜是对应的,对不对? 那对地位是和那个SP相对应的出来,这个十十个扣的地位是不一样的,最高位的权重实际上要乘以512的,所以我们要把刚刚的时配要乘以它对应的权重,那对于MSD这边呢,也就是根号下1/512加1/512,在乘以外面那个512,那这个时候等一下为多少呢。 等一下为根号下的1024,然后我们再看SBLS这边LSB这边呢,刚刚算的那个十倍是多少,贡献的十倍是一嘛,对不对? 那它的权重也是一也是一,那一乘以一就是一,那这个时候就出现什么,大家会发现呢,就说MSB这边的权,这这边的适配虽然小,但是乘以它权重以后就显得大。 这个为什么会这样呢? 那就是因为我们这个权重是在二进制变化,然后随着权重的提升,我们的适配在什么什么,它只是在以这个以跟二这种倍数在在在改变它就说这两个比例会不一样,所以就说电容越大的话,它那个就是其实相对精度,它是它是不够的啊。 那这种理解是那种我认为相对比较那种稍微直观一点的啊,这种或者感性的理解啊,那真正的需要的还是要去从那个DL的那个表达式里面去看,那那个理解可能更更严谨一些。 问8a 在跑蒙特卡罗的时候,器件model选带mc的,这种和tt,ss,ff有什么区别,跑蒙特卡罗的时候有一个prosess和mismatch,这个process和corner角有什么区别。 我仿真出来的3segma的偏差是典型值的么 还是最大值? 总体而言,有电荷泵的电路寿命确实也会受到影响,或多或少而已,但这种差别一般是30年和20年的差别。 对于一般的民用产品,一个手机用几年而已,轮不到器失效。 如果对产品寿命要求极高,需要谨慎评估相关电路结构。 A: 是,你说的对,上下各偏移0.5 秋冬季节很干燥,我们手触摸到物品也会发生尖端放电,这瞬间的电压也是很高的,我们只是手麻那么一下,只是因为总能量太低了,不足以致死。 反而220V这种不高的电压持续施加给人体,人会受不了。 总体而言,有电荷泵的电路寿命确实也会受到影响,或多或少而已,但这种差别一般是30年和20年的差别。 对于一般的民用产品,一个手机用几年而已,轮不到器失效。 如果对产品寿命要求极高,需要谨慎评估相关电路结构。 问8b

这个地方是不是不对,应该是-0.5LSB~2^(N)-0.5 上下各偏移0.5。 问9 差分采样是否就能很好的抑制时钟馈通对信号的影响? 时钟馈通说的是寄生电容的分压,沟道电荷是MOS开启时候沟道内的载流子在MOS关断以后的再分配,一般是S和D各自分一点,具体怎么分还得看CLK的下降沿速度。 process就是同一个器件性能呈现出的概率分布,mismatch就是不同位置的同类型器件之间差异的分布。 小电容,电路带宽高,高频更容易通过。 差分减弱大部分,不能完全消除时钟馈通和沟道电荷的影响。 因为仔细分析你会发现这2个效应和信号大小相关,而全差分信号在同一时刻信号大小是不一样的。 如果简单的全差分就能完全消除时钟馈通和沟道电荷,那上级版采样就不存在精度不高的问题了。 对于10bit以下的高速ADC来说,似乎全差分设计,就差不多够用。 下极板采样配合全差分才能真正做到高精度采样 7~8bit,这么说可能也不太准确,还是要看具体设计 我们在SMIC 14nm和28nm工艺下的10Bit,对比了上极板采样和下极板采样,测试结果显示速度能跑到100MHz+,ENOB在9.7Bit附近,和采样技术没啥关系。 主要瓶颈其实是在Latch比较器噪声。 (责任编辑:admin) |