|

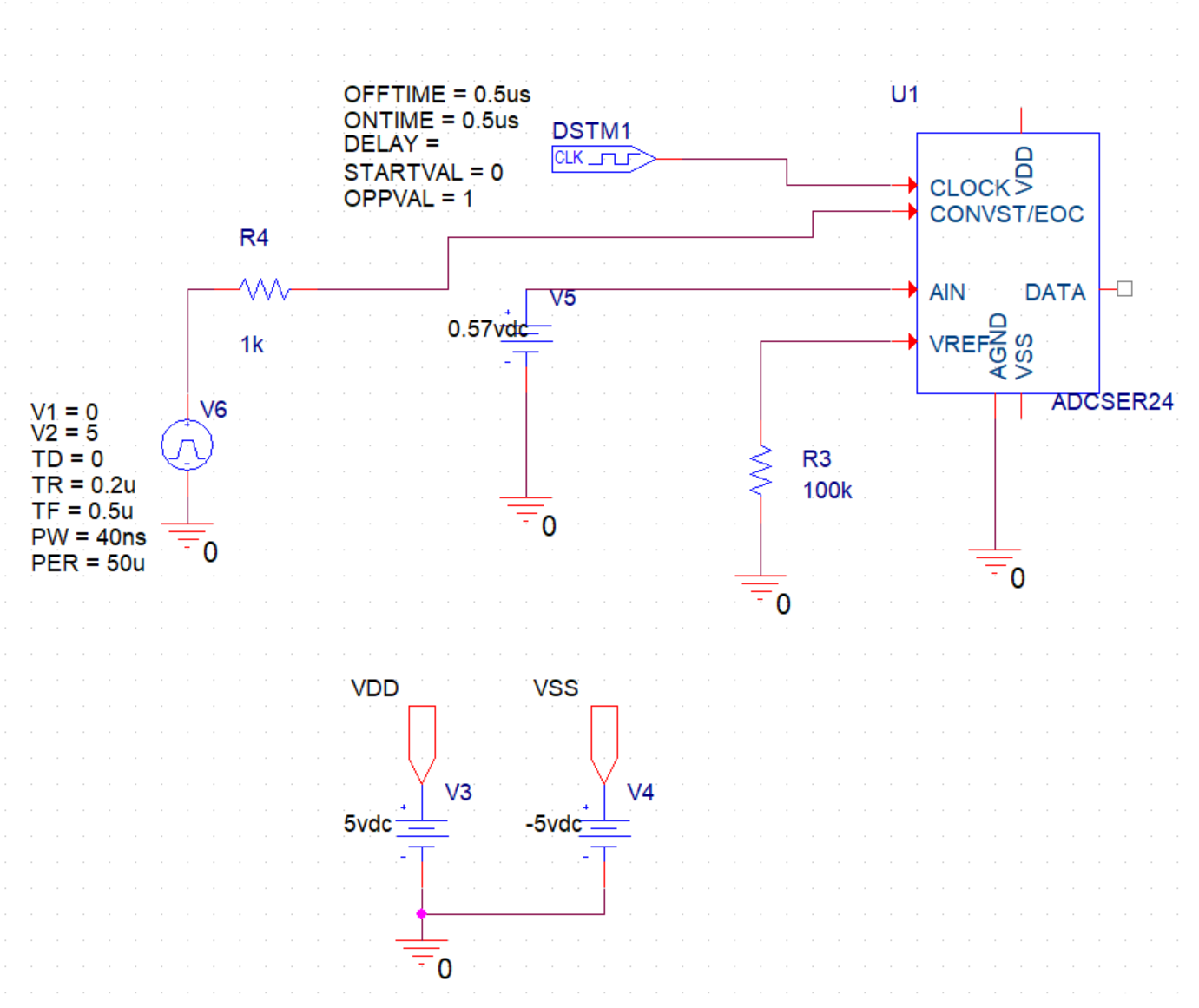

在Capture中打开ADC_DEMO.opj,把U1替换成ADCSER24,原理图如下:

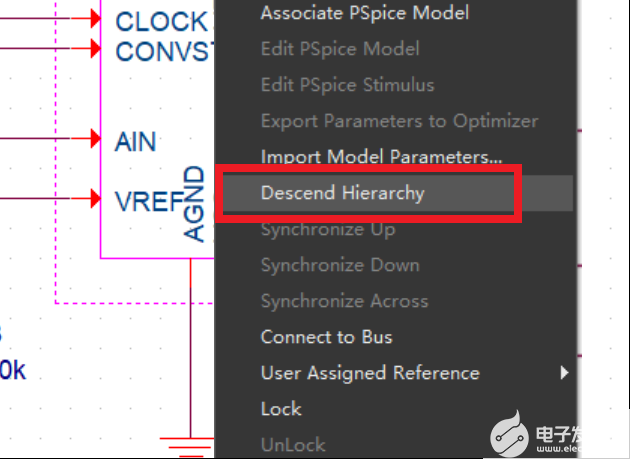

选中AD转换器,点击鼠标右键,选择Desend Hierarchy,可以进入查看AD转换器的内部模型。

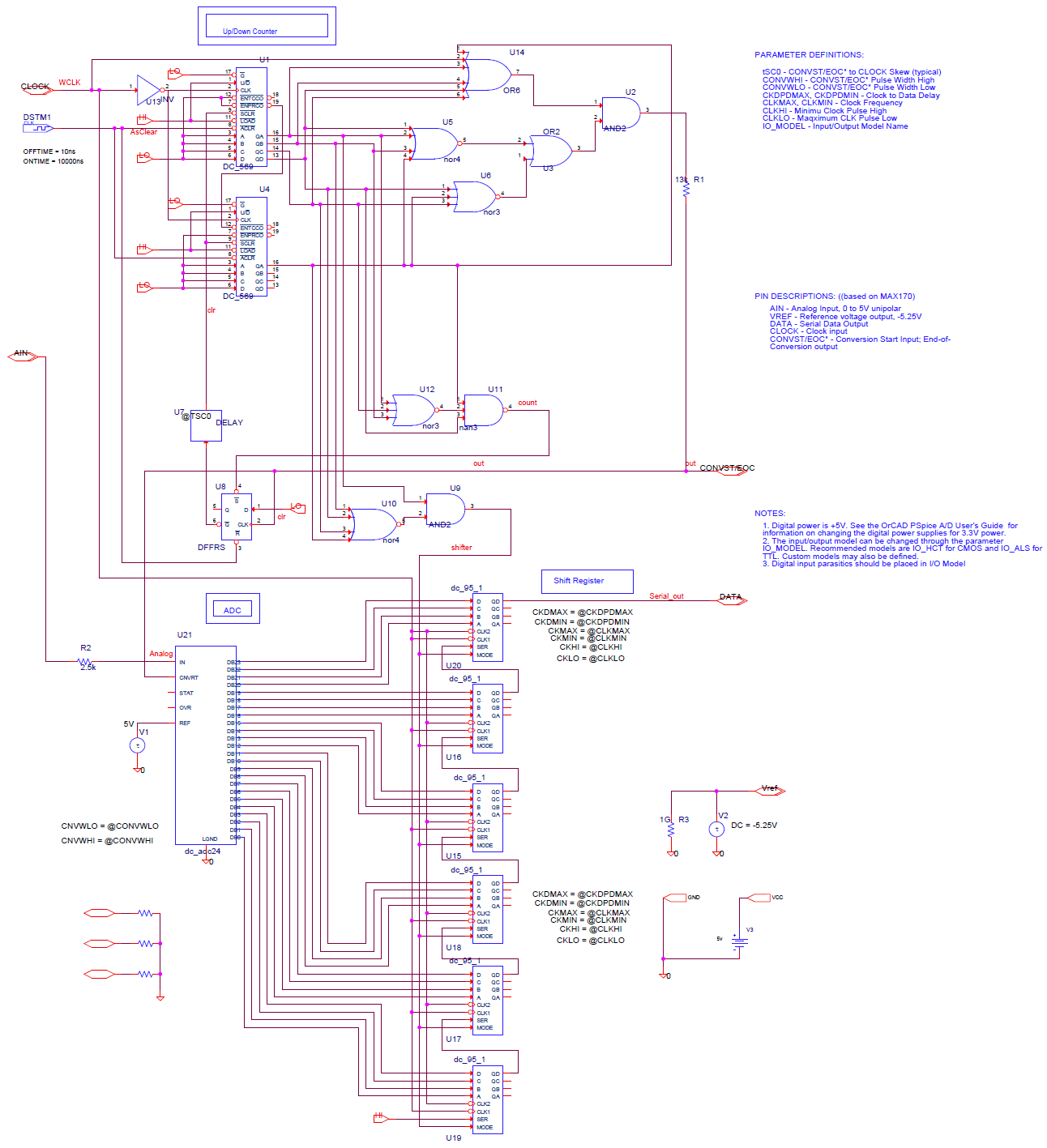

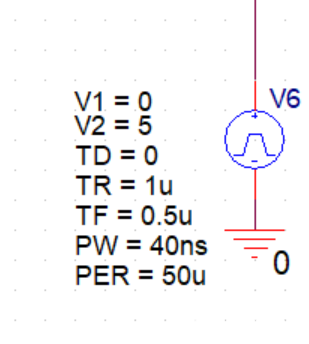

从内部原理图中,不难看出,pspice中提供的ADCSER24,与ADCSER4一样,同样是把模拟数据先转换成并行的数字数据,再用D寄存器串行输出。 其中: AIN – Analog Input, 0 to 5V unipolar(0-5V的模拟输入信号) VREF – Reference voltage output, -5.25V(参考电压,输出) DATA – Serial Data Output(串行数据输出) CLOCK – Clock input(时钟信号输入,要求小于5Meg,大于178.571K) CONVST/EOC* – Conversion Start Input; End-of-Conversion output(使能信号——开始转换,转换结束) 在这个实验中,我们把CLK信号定义为1Meg,Ain采用直流信号输入,CONVST/EOC——使用脉冲信号,周期为50us。

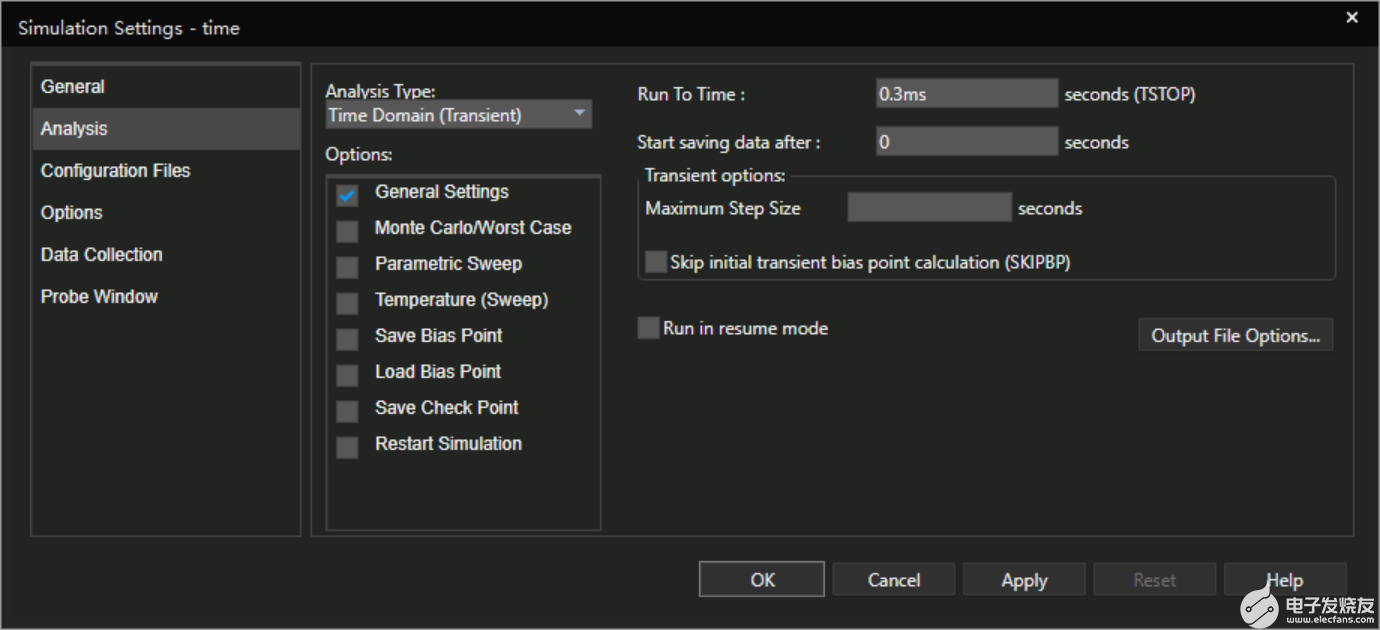

根据上一次碰上的问题,直接先检查DC_95_1这个元件的PspiceTemplate属性,如果有问题,直接修正。 创建仿真分析文件,进行时域仿真:

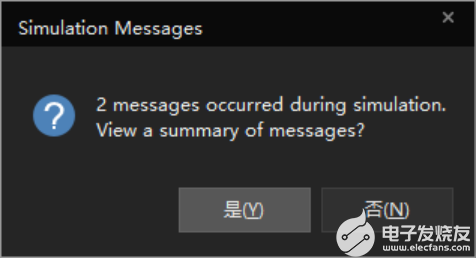

仿真时间定为0.3ms,启动仿真。 Pspice仿真完后,弹出如下信息提醒框:

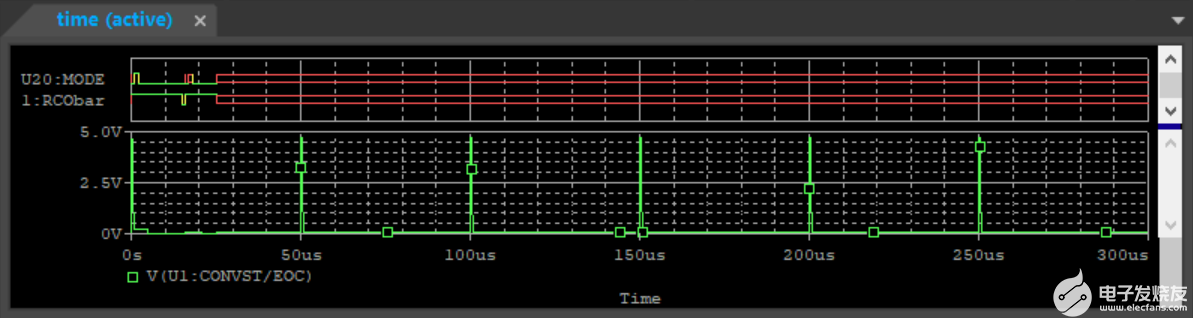

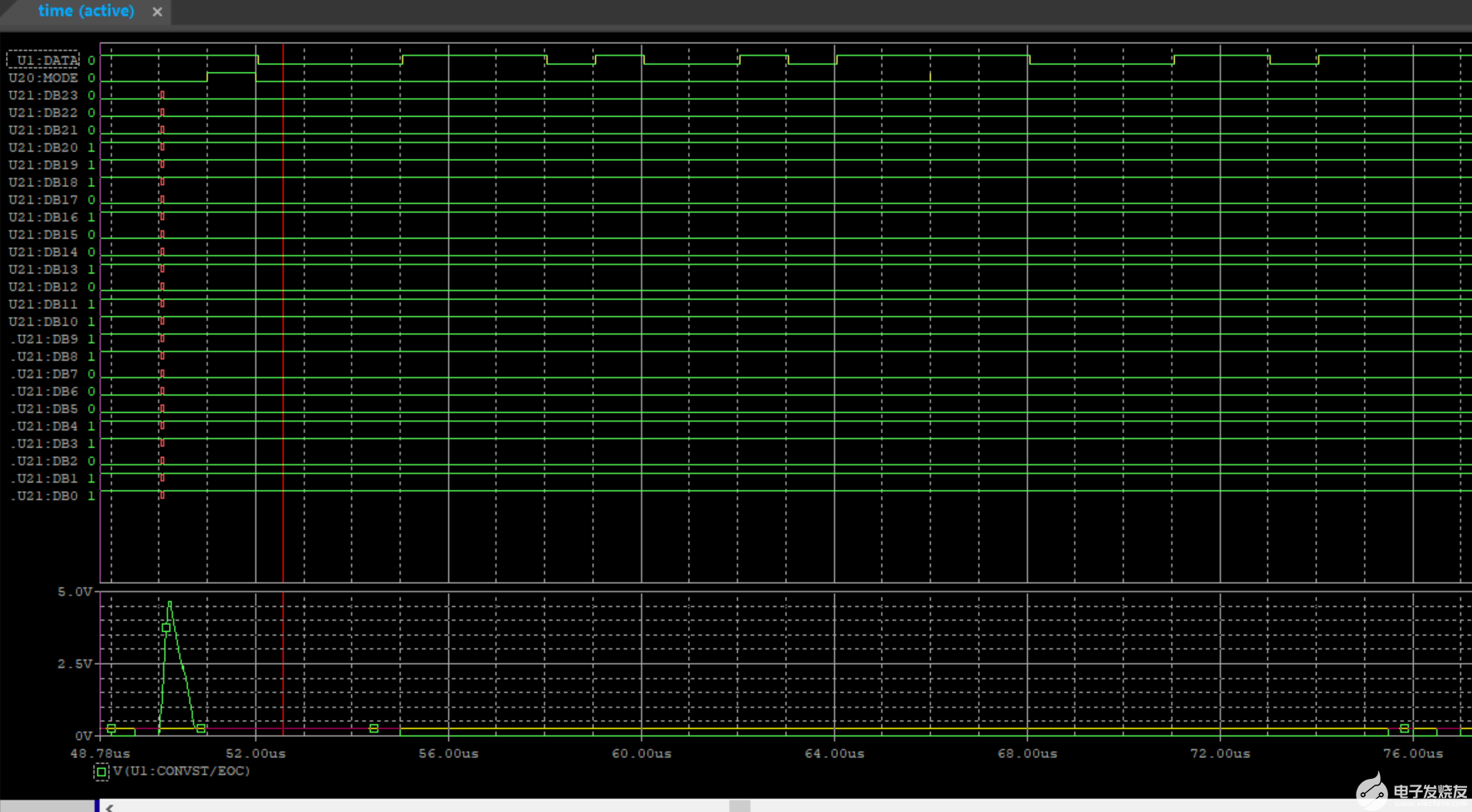

选择“否”,并查看DATA的输出,图形如下:

可以看出,DATA串行输出有问题,仿真不正常。 重新运行仿真,弹出信息提醒框后,点击“是”,进入查看。

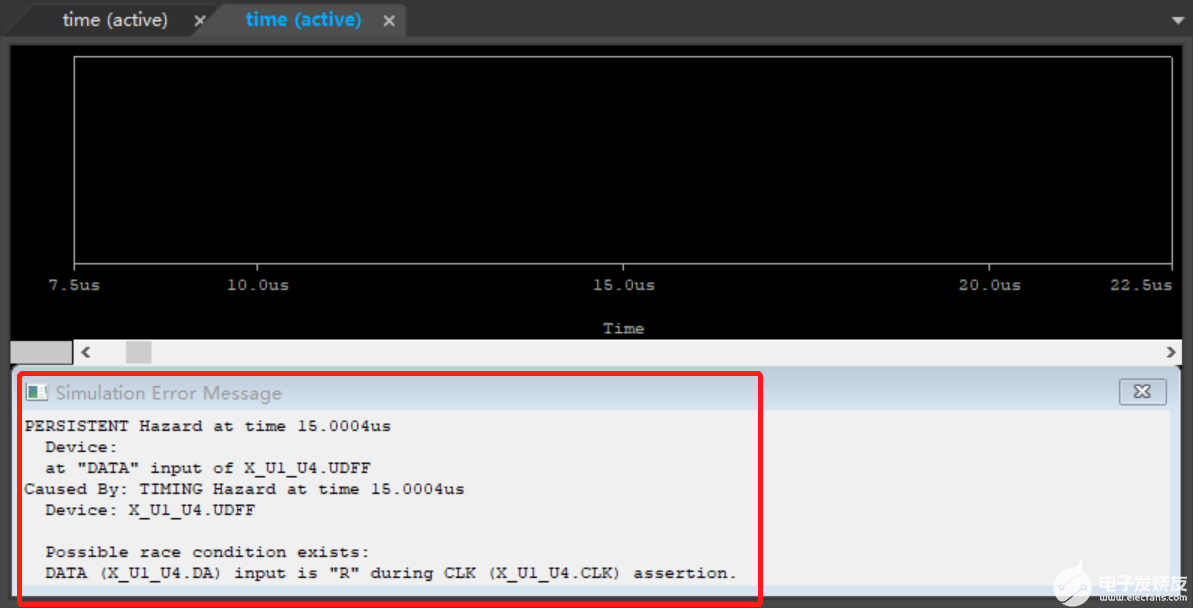

点击Plot,显示出Error信息窗口:

分析错误信息,发现是U1.U4的输入在上升沿与时钟的时序冲突,详细分析原理图,发现U1.U1与U1.U4是一样的,唯一的区别是U1.U4的ENT信号是从U1.U1的RCO取得的,估计是这个信号进行X状态,导致的。 因此,在U1.U4的ENT输入加100K的下拉电阻。 再次仿真,跳过提示,查看DATA输出结果: 注:pspice中,数字信号分为0、1、R(上升沿)、X(状态不定)、F(下降沿)五种状态。

|