|

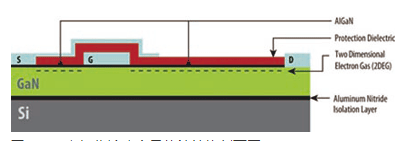

我们对功率半导体最基本的要求是性能、可靠性、管控性及成本效益。它的高频率性能,可切合稳压器系统于体积及瞬态响应方面的需要而具更高价值,并为 D类功率放大器提供高保真度。一个新器件结构如果不高效、不可靠的话,根本不可能商品化。市场上有很多新结构及原料可选择,但是接受度有限。不过,现在有氮化镓(Gallium Nitride/GaN)增强型功率管控器件问世,具有高导电性、极快开关、硅器件之成本结构及基本操作模式等优异性能,其代表就是宜普公司的新产品。 器件构造 一个器件的成本效益,从生产基础设施开始计算。宜普公司的工艺技术,基于不昂贵的硅晶园片。在硅基板上有一层薄薄的氮化铝 (Aluminum Nitride/Al),隔离了器件结构和基底。这个隔离层能隔离300V电压。在这隔离层上是一层厚厚的氮化镓,晶体管就建立于这个基础上。其中,电子由氮化镓铝层(AlGaN)产生,其会产生引力场,吸引大量的自由浮动电子,而进一步的工艺会在栅极下面形成一个耗尽区域。要增强晶体管,正电压加在栅极处,正如开启一个N通道、增强型之功率MOSFET。 图1显示了这个器件结构的剖面图。该器件的表现跟硅功率MOSFET相似,当然也有不同之处,我们将再作阐释。

图1 EPC之氮化镓功率晶体管结构剖面图 操作 宜普氮化镓晶体管的表现跟硅功率MOSFET非常相似。在栅极上,相对于源极,一个正偏压会产生吸引电子的场效应,构成基极与源极之间的通道。由于电子被集中在一起,不会零散地困于某一格位置,这个通道的电阻因而很低。从栅极移去偏压,下面的电子会分散至氮化镓层,重新产生耗尽区域,从而阻隔电压。 要制成一个高压器件,需增加漏极与栅极之间的距离。由于氮化镓的电子被集中在一起时的电阻非常低,所以纵使增加阻隔电压之能力,若与硅器件相比,其对电阻的影响会更少。图2显示了理论上的氮化镓及硅器件于不同电压下的性能极限,及宜普第一代器件的效能。 各位电子工程界朋友均知道硅制MOSFET已开发了三十年,其表现已接近理论上的极限,若希望其表现再进一小步,将需要庞大资源去开发。相对来说,氮化镓器件处于产品发展周期的起步阶段,在数年内将可预见其重大进展。

图2 氮化镓及硅器件于不同电压下的性能 栅极临界 氮化镓晶体管的临界比硅功率MOSFET低,这样是有可能的,因为临界不会随温度变化及具备很低的栅漏极间电容(CGD)。 图3显示了宜普1001(100V,5.6mΩ)的晶体管传输特征曲线。当器件在1.6V电压时开始传导大量电流,于dv/dt转变时,栅极到源极之间为低电阻。

图3 传输特征曲线图 电阻 阻抗(RDS(on))及栅源电压(VGS)曲线图是跟MOSFET相似的。宜普第一代氮化镓晶体管专为5V驱动器操作而设。 图 4显示了宜普1001的一系列曲线图。当栅极电压越接近最高水平,漏极对源极的电阻则会持续下降。由于栅极驱动器损耗极少,所以氮化镓晶体管应以5V电压驱动。氮化镓晶体管之电阻RDS(on) 温度系数为正数,但幅度比硅MOSFET小很多,例如,在125℃时,宜普1001系数为25℃时的1.45倍,而硅功率MOSFET则是1.7倍。这个优势会随着电压增加而增强。

图4 不同电流下RDS(on)与VGS的比较 电容 氮化镓晶体管的横向结构使其具极低电荷特性,能够在数纳秒内切换数百伏特,切换频率可达数兆赫,这个性能可缩小功率转换器体积,并使D类功率放大器具更高的保真度。栅漏极间电容(CGD)是最重要的,因为它最能影响切换功率损耗。宜普氮化镓场效应晶体管因为具极低CGD,致使电压切换非常迅速。相比CGD,栅源极间电容(CGS)较大,使氮化镓晶体管拥优异的dV/dt抗扰性能。相比硅MOSFET,栅源极间电容(CGS)较小,延迟时间很短,因此应用于低负载周期时具极佳管控能力。 根据实例证明,一个1~48V降压稳压器使用宜普之100V氮化镓晶体管,可于1MHz切换频率下表现理想。与硅MOSFET比较,氮化镓晶体管之CDS也较小,虽然二者之电容曲线相似,但在相同电阻下,最大不同之处是氮化镓晶体管之电容是极低的。 串联栅极电阻及栅极漏电流 串联栅极电阻(RG)限制了FET的电容充电或放电速度。硅MOSFET只能用多晶硅或混合材料类的金属硅化物;氮化镓晶体管则用金属栅极,栅极的电阻很低,只是1/20Ω,具dV/dt抗扰能力,并且不会以氧化增生来隔离栅极。相比硅MOSFET,氮化镓晶体管栅极漏电流较大,预计在1mA。 优异指标 总栅极电荷(QG)是CGS加CGD除以电压。常用的指标FOM是RDS(on)乘以QG,显示了器件在开启状态及切换时的表现。图5展示了氮化镓晶体管与最优异硅MOSFET 100V器件之FOM比较。当电压增加,其RxQ FOM更具优势。

图5 氮化镓晶体管与最优异100V硅MOSFET器件之FOM比较 基板二极管 从图1可见,宜普氮化镓晶体管结构是一个横向器件,没有硅MOSFET常见的寄生二极接面。严格来说,其反向偏压与二极管具相似功能但机理不同。如果栅源电压是零偏压,栅极下方就没有电子。当电流从源极至漏极,漏极电压会减弱。相比飘移区域,栅极上正偏压形成后会把电子注入栅极下面。在栅极临界时,将有足够电子形成一个传导通道,其好处是在传导中没有少数载流子,所以没有反向恢复损耗。当QRR是0时,输出电容COSS需要在每次开关周期内充电或放电。相比硅MOSFET,若器件的RDS(on)相仿,则氮化镓晶体管具更低的COSS。氮化镓晶体管在反向时需临界电压去开启,二极管之正向电压会比硅晶体管为高,所以必需把二极管导电减至最小。 封装 宜普氮化镓晶体管与底层绝缘,可以在单晶圆上制造多个不同配置,快速散热及不需绝缘接口之晶体管。它可以在晶圆片的一边凑集漏极及源极电流。若果要凑集电流的金属层具低电阻,这些通道必需短小。要做到这样,可利用芯片线栅门数组封装,把漏极及源极线交替排列。标准的线距是0.4mm及 0.6mm。图6展示了宜普1010晶体管封装(200V,25mΩ)。如果任何部份之沿面放电距离不能达到安全要求,可用underfill方法来达到其所需安全距离。

图6 宜普1010晶体管 应用及价值 宜普设计的增强型氮化镓晶体管,具有高效、高频、低负载周期功率转换的优势。其可于频率高于AM band时,透过高效开关,大幅提升D类功效音频放大器技术。因没有线性放大器之体积及重量的所有限制,保真度可接近A类及AB类放大器系统水平,并可把高质素放大器放进只有细小器件空间的产品里,如平面电视、电脑及扬声器。 于处理信息及储存系统方面,整个功率架构可重新评估,以发挥其优异的开关性能。当AC/DC转换器输出电压增加,效率会更高;当总线电压增加,传输效率会提高;当频率增加,体积会更小。如果应用为同步整流器,可同时提高AC /DC转换效率。如果只是一次转换,可撤用中间阶段转换器,省却中间阶段转换器之体积及成本。 审核编辑 :李倩 (责任编辑:admin) |