|

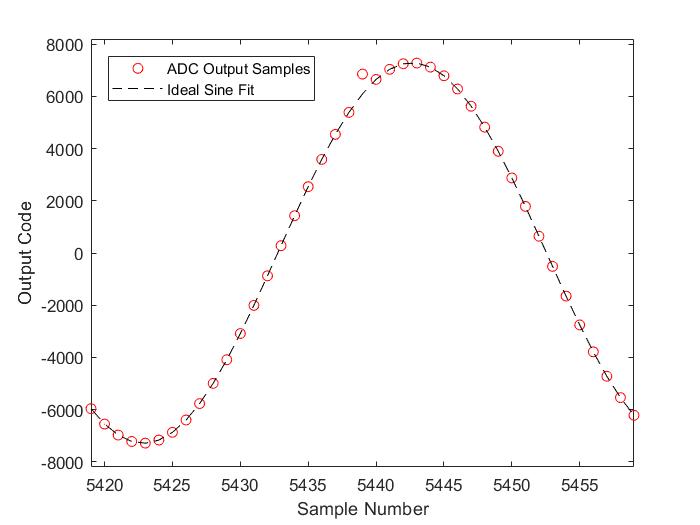

随着高速模数转换器 (ADC) 采样率的提高,ADC 输出数据中的代码错误(也称为闪码)问题也随之增加。代码错误定义为 ADC 输出代码中的错误超过定义的阈值。阈值通常定义为误差超过 ADC 噪声预期幅度的电平,以便在存在噪声的情况下可以轻松识别误差。 解释误差阈值定义的另一种方法是,误差幅度的发生概率超过给定 ADC 假设的高斯分布噪声的幅度的预期概率。图 1显示了在 ADC 的输出样本中发现的示例代码错误。与理想的正弦波拟合相比,错误样本清晰可见,并且远远超过图中其他样本的噪声。

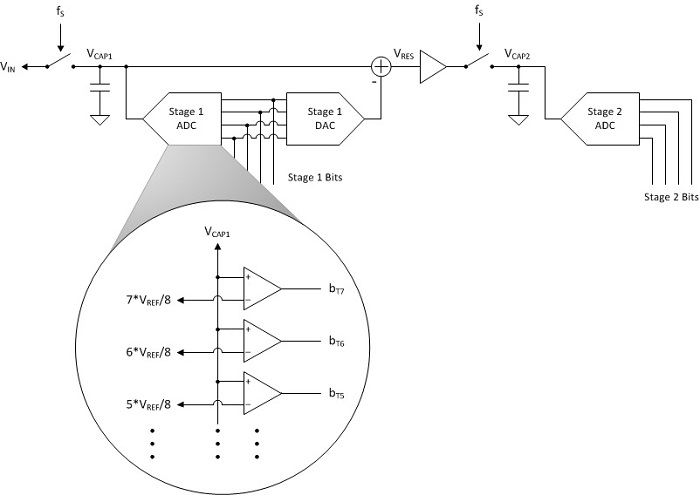

图 1:带有代码错误的 ADC 输出示例。 ADC 的代码错误率 (CER),有时也称为字错误率 (WER) 或亚稳态错误率,定义为每个样本的平均错误数,通过计算连续错误之间的平均样本数来测量。它通常被定义为一个数量级,例如 10 –12个错误/样本。因此,错误之间的平均时间取决于转换器的采样率。只有当 ADC 以测量 CER 的采样率运行时,测量的 CER 才是准确的。一般来说,降低采样率可以将 CER 提高几个数量级。 让我们看看代码错误来自哪里,看看为什么采样率是一个主要因素。 是什么让 ADC 闪闪发光? 多步 ADC 架构,例如流水线闪存 ADC 或逐次逼近寄存器 (SAR) ADC,将采样电压分阶段转换为数字位,每个连续阶段都依赖于前一阶段的结果。考虑一个基本的流水线闪存高速 ADC,如图2 所示。这个简化的 ADC 显示了两个转换阶段,其中每个连续的阶段产生一个数字代码,可以更精细地估计输入信号。 所示 ADC 的操作如下: 第一级对输入电压进行采样,并使用第一级 ADC 将模拟输入信号粗略转换为数字代码。此阶段的闪存 ADC 通过使用高速比较器将采样电压与由 ADC 的主参考电压 (V REF ) 生成的静态参考电压进行比较来工作。闪光比较器的输出是代表输入电压的温度计编码数字样本。 然后将转换后的温度计代码直接发送到第一级 DAC。该 DAC 输出模拟电压,对应于粗略转换的样本。 从原始输入电压中减去第一级 DAC 的输出,得到量化误差电压或残余电压 (V RES )。然后将残留物放大并重新采样(流水线)用于第二阶段。 第二级 ADC 量化 V RES以获得对原始模拟输入电压的更准确(更高分辨率)的估计。

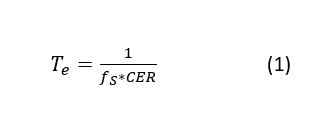

图 2:流水线闪存 ADC 架构框图示例。 V RES创建过程引入了一个高速决策循环。在一个采样时钟周期内,采样电压必须由第一级 ADC 转换为数字代码。数字代码必须从第一级 DAC 输出,从原始输入电压中减去并由第二级重新采样。高速决策环路会引入代码错误,因为闪存 ADC 中的比较器有一个稳定时间,该时间是采样电压和VREF之差的函数。 更简单地说,当输入电压(V CAP1)接近比较器的参考电压(例如 7 * V REF /8)时,比较器需要更长的时间来稳定。理论上,如果 V CAP1无限接近比较器的参考电压,则比较器将永远不会稳定,因为它将工作在其线性区域。 噪声会阻止这种情况实际发生,但如果比较器确实需要很长时间才能稳定,那么第一级 DAC 可能会使用不正确的数字代码来输出量化的模拟电压。结果是 V RES与第一级 ADC 的实际数字输出代码不匹配。然后,第二级 ADC 转换错误的 V RES,从而导致代码错误。 什么影响 CER? 您现在应该有足够的详细信息,以便能够就影响 CER 的因素得出一些结论。CER 显然取决于采样率。更快的采样率减少了决策循环必须做出决策的时间。更短的决策时间导致比较器未及时稳定的概率呈指数增长。1另请注意,比较器的速度直接影响 CER,这是构建 ADC 的工艺技术的一个强大功能。第三个因素是 ADC 的架构。 具有高速决策循环的多步架构容易受到较差 CER 的影响。有一些技术可用于降低这些架构的 CER,例如使用更快的处理技术、实施时间交错或采用异步时钟。2, 3另一方面,不使用高速决策回路的架构,例如折叠插值架构,可以使用多个比较器重新锁存级而不影响任何后续级,从而大大降低亚稳态的概率。4 因此,与类似的流水线闪存或 SAR ADC 架构相比,单步架构本质上具有更好的 CER。具有决策回路的多步架构不能在没有相应速度降低的情况下使用比较器重新锁定。 代码错误影响的示例 让我们看一个代码错误如何影响示波器测量的示例。假设 RS-485 发射器间歇性地输出毛刺,工程团队正试图在示波器上测量该毛刺以找出根本原因。假设毛刺很小,每隔几天发生一次,并且示波器使用简单的电压阈值检测。还假设示波器以 10 GSPS 的速率进行采样,并且代码错误率为 10 –12个错误/样本。您是否更有可能从发射器中发现故障或从 ADC 中发现代码错误?让我们来了解一下! 误差之间的平均时间(以秒为单位)是 T e,您可以根据公式 1 从 CER 和 ADC 采样率 (f S ) 计算得出:

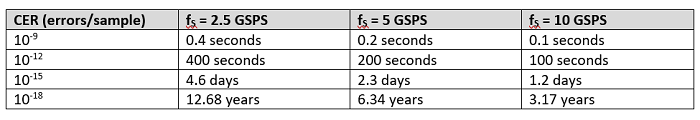

以上面的 RS-485 毛刺示例为例,示波器的平均误差间隔时间计算为 100 秒。如果每隔几天就会出现 RS-485 毛刺,那么将很难从被测设备中捕获所需的毛刺,因为示波器将持续触发代码错误。 那么什么 CER 是可以接受的呢?表 1显示了各种错误率和采样率的平均错误间隔时间。在 10 GSPS 时,需要远低于 10 –15 的代码错误率才能捕获每隔几天发生的故障。使用折叠插值 ADC 构建的示波器(例如ADC12DJ5200RF)很有可能捕捉到毛刺,而不会因为其 10 –18的低 CER 而导致间歇性代码错误导致误触发。

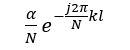

表 1:T e与 CER 和采样率的关系。 代码错误对高速 ADC 应用有不同程度的影响。示波器和基于脉冲的飞行时间 (ToF) 系统(例如 LiDAR 或激光距离测量)在使用简单阈值检测时可能对代码错误更敏感,而通信或雷达系统可能不太敏感。 例如,通信系统经常使用前向纠错 (FEC),它可以克服 ADC 样本数据中单个代码错误的影响。雷达使用基于匹配滤波器(相关)的检测算法,该算法使用长波形来提高检测精度,从而从本质上减轻单个代码错误的影响。 频域中 的代码错误 代码错误的频谱,如离散傅里叶变换 (DFT) 的输出所示,是在所有频率区间均值相等的升高的本底噪声。下面的计算从输出 X k的归一化 DFT 的定义开始,到出现代码错误时的输出频谱 Y k。这

Y k中的项是在时域信号中表示为脉冲的单个码错误的频率贡献。真实 DFT 的本底噪声功率提高了

它与误码幅度的平方 α 2成正比,与 DFT 的平方长度 N 2成反比。因此,使用较长信号长度或分析窗口的系统将受到代码错误的影响较小。

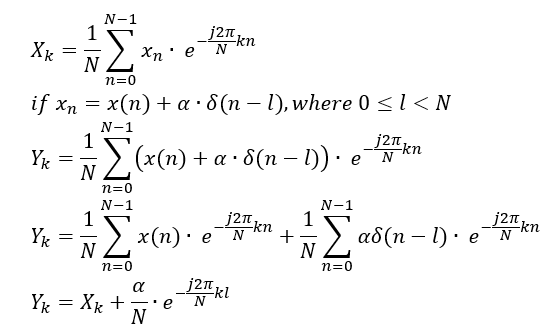

图3说明了由图1中的码错误引起的升高的本底噪声,其幅度为758码。在将结果归一化为 14 位转换器的满量程功率后,对于长度为 65,536 的实际 DFT 计算得出的每个 bin 的噪声功率为 –110.98 dBFS/bin,

该结果与图 3中被代码错误破坏的测量的本底噪声相匹配。

图 3:有和没有代码错误的频域。 结论代码错误在 高速 ADC的时域输出中表现为不需要的脉冲。在频域中,使用 DFT 进行测量,代码错误会导致本底噪声升高。虽然某些应用程序可以忍受这些代码错误,但其他应用程序(例如示波器或基于脉冲的 ToF)需要低错误率才能成功。 代码错误是多步 ADC 架构中比较器亚稳态的结果,需要在前一阶段快速做出高速决策,以便下一阶段使用结果。采样率、比较器速度和 ADC 架构会影响 ADC 设计的 CER。 不需要高速决策环路的 ADC 架构(例如折叠插值架构)本身就具有更好的 CER,因为它们能够重新锁定比较器输出,从而在没有相应速度降低的情况下降低亚稳态概率。 ADC12DJ5200RF是一款超高速 ADC,提供业内最低的可用 CER,使工程师能够为测试和测量应用实现高测量信心。 审核编辑:汤梓红 (责任编辑:admin) |