|

工程上常用ADS进行射频功率放大器裸芯片电路级设计,然后将裸芯电路原理图或版图与设计好的基板进行联合仿真。常用的裸芯与基板联合仿真方法包括使用ADS + Momentum或ADS嵌套技术或ADS+HFSS等。由于射频电路的实际寄生很难准确模拟,在射频功率放大器芯片的设计研制过程中,工程师们常对应采用什么样的基板联合仿真方法感到困惑。

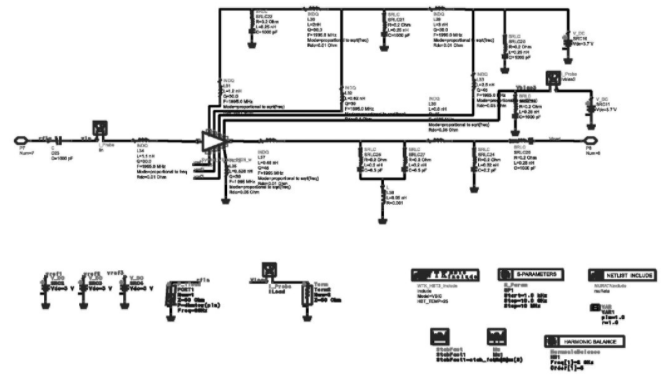

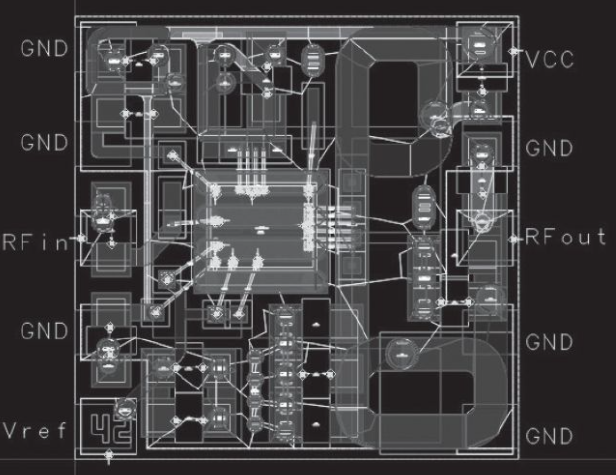

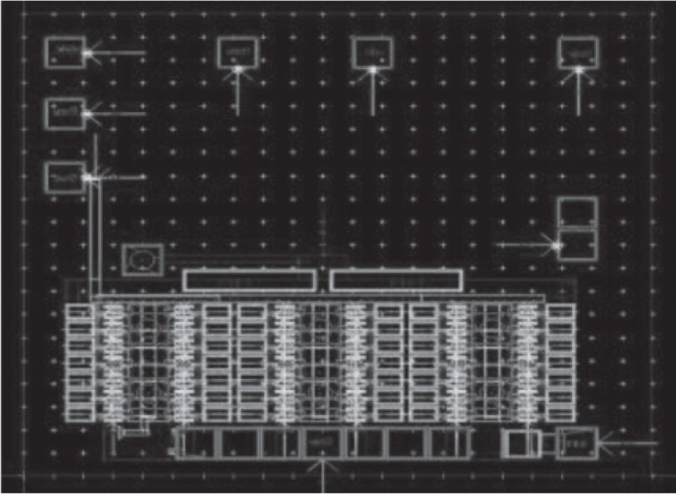

本文以自主研制的工作频率2GHz的射频功率放大器芯片为例,从仿真器的算法理论、联合仿真的具体建模方法、建模复杂度、仿真时间、对比实测结果等几个方面对上述几种常用的基板联合仿真方法进行了比较探讨,尝试归纳总结出对实际射频功率放大器芯片工程设计有帮助的仿真经验。 引言 工程上常用ADS进行射频功率放大器(PA)裸芯片(Die) 电路级设计。为了提高仿真准确度,会将裸芯电路原理图或版图与设计好的基板进行联合仿真。常用的裸芯与基板联合仿真方法包括使用ADS+Momentum或ADS嵌套技术(Nested Technology)或ADS+HFSS等。由于射频电路的实际寄生很难准确模拟,在射频功率放大器芯片的设计研制过程中,工程师们常对应采用什么样的基板联合仿真方法感到困惑。本文以利用ADS2014和HFSS 15.0自主研制的工作频率2GHz的射频功率放大器芯片(PA#L03)为例,从仿真器的算法理论、联合仿真的具体建模方法、建模复杂度、仿真时间、对比实测结果等几个方面对上述几种常用的基板联合仿真方法进行了比较探讨,尝试归纳总结出对实际射频功率放大器芯片工程设计有帮助的仿真经验。 本例射频功率放大器芯片PA#L03的电路设计原理图(顶层)如图1所示。

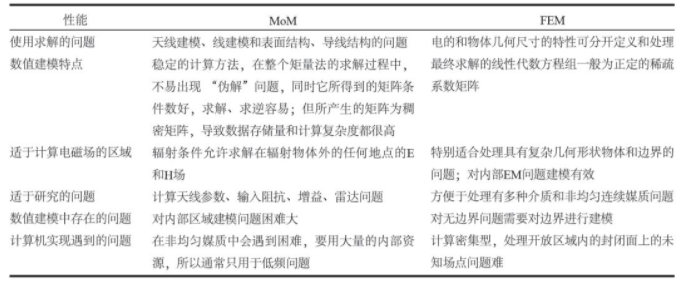

1 各种仿真器算法比较 ADS是由美国安捷伦(Agilent)公司推出的一款基于矩量法(MoM)的射频电路仿真工具,它的EM 仿真器包括Momentum Microwave和FEM。其中Momentum的算法基于矩量法(MoM,Method of Moment),FEM的算法基于有限元法(FEM,FiniteElement Method)。HFSS是Ansoft公司推出的基于有限元法的针对高频结构的电磁仿真软件。下面扼要介绍一下矩量法和有限元法[1,2]。 (1)有限元法(FEM) 有限元方法是在20世纪40年代被提出,后来这种方法得到发展并被非常广泛地应用于结构分析问题中。有限元法是以变分原理为基础的一种数值计算方法。应用变分原理,把所要求解的边值问题转化为相应的变分问题,利用对场域的剖分、插值离散化变分问题为普通多元函数的极值问题, 进而得到一组多元的代数方程组, 求解代数方程组就可以得到所求边值问题的数值解。一般要经过如下步骤: ①区域离散化。即将场域或物体分为有限个子域,如三角形、四边形、四面体、六面体等; ②选择插值函数。选择插值函数的类型如多项式,用结点(图形定点)的场值求取子域各点的场的近似值。插值函数可以选择为一阶(线性)、二阶(二次)、或高阶多项式。尽管高阶多项式的精度高,但通常得到的公式也比较复杂; ③方程组公式的建立。可以通过里兹方法或者迦辽金方法建立; ④ 选择合适的代数解法求解代数方程, 即可得到待求边值问题的数值解。 (2)矩量法(MoM) 矩量法是计算电磁学中最为常用的方法之一。自从20世纪60年代Harrington提出矩量法的基本概念以来,它在理论上日臻完善,并广泛地应用于工程之中。特别是在电磁辐射与散射及电磁兼容领域,矩量法更显示出其独特的优越性。矩量法的基本思想是将几何目标剖分离散,在其上定义合适的基函数,然后建立积分方程,用权函数检验从而产生一个矩阵方程,求解该矩阵方程,即可得到几何目标上的电流分布,从而其他近远场信息可从该电流分布求得。 根据算法原理,表1归纳对比了MoM和FEM两种算法的性能特点。 至于ADS自带的FEM仿真器与HFSS的FEM仿真器,算法原理上并无大区别,但在软件算法引擎程序的具体实现方法以及边界条件的设定上有区别。此外,ADS 可以仿真有源器件而HFSS不能。

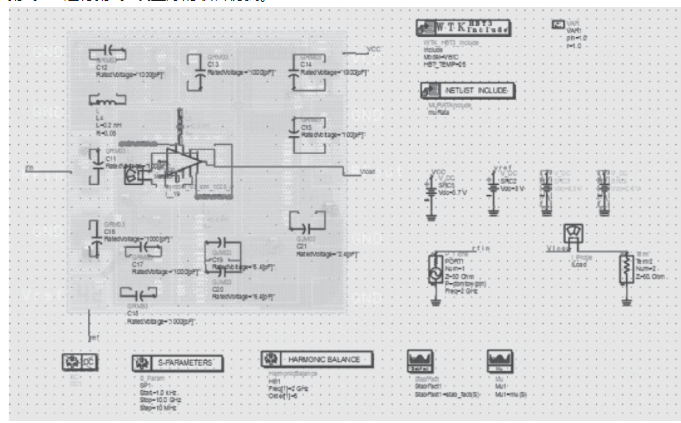

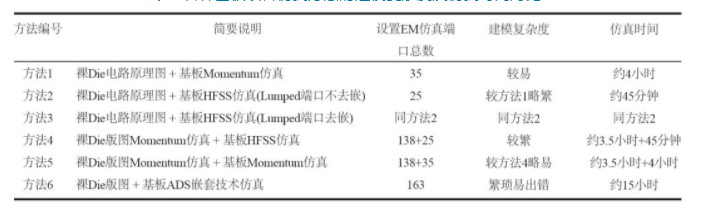

表1 MoM和FEM两种算法的性能特点对比 2 各种基板联合仿真的具体建模方法 和相应建模复杂度及仿真时间对比本文作者从实际工程经验中总结出以下几种射频功率放大器裸芯和基板联合仿真方法:具体的辅助软件操作方法可参考[2,3]。 方法1 : 裸D i e 电路原理图 + 基板Momentum仿真 第1步:在ADS里,将设计好的PA基板版图(layout)在钩挂有源器件、无源器件、外接电源处进行ADS端口(PORT)设置,如图2(a)所示。所创建的基板EM衬底文件(.subst)如图2(b)所示。 第2步:在进行ADS EM 仿真设置时,要创建Symbol并选择Symbol类型为Layout look-like,运行Momentum Microwave EM 仿真。仿真完毕会自动更新Symbol。 第3步:在ADS原理图里,将第2步所仿真好的PA基板版图Symbol与封装在Symbol里的PA 裸Die电路钩挂起来,如图3所示。 第4步:运行第3步设置好的联合仿真。

(a) 基板Momentum仿真端口设置

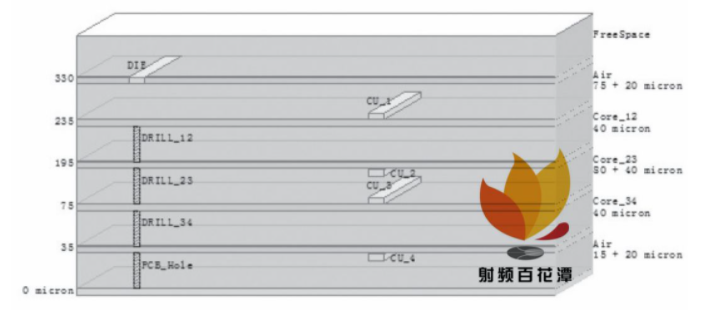

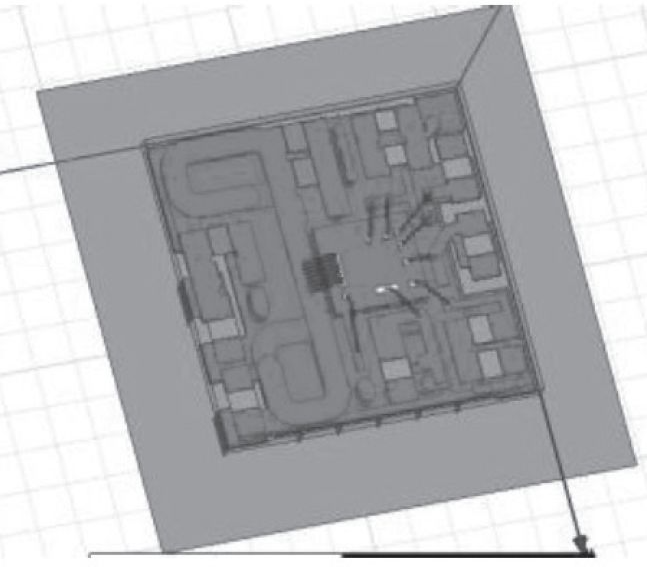

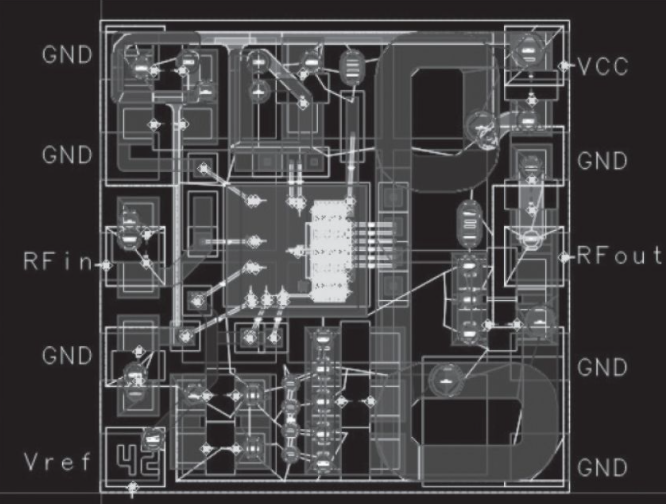

(b) 基板EM衬底设置 图2 基板Momentum 仿真设置和创建的基板EM衬底文件 方法2:裸Die电路原理图 + 基板HFSS仿真(Lumped端口不去嵌) 第1步:在ADS里,将设计好的PA基板版图(layout)导入到HFSS里建模。在钩挂有源器件、无源器件、外接电源处进行HFSS集总端口(LumpedPORT)设置,如图4所示。方法2中的Lumped端口不去嵌(Deembed)。 第2步:运行HFSS仿真,仿真完毕后导出N端口S参数文件(.SNP)。 第3步:在ADS原理图里,将第2步HFSS仿真所得到的PA基板版图S参数文件与封装在Symbol里的PA 裸Die电路钩挂起来,如图5所示。 第4步:运行第3步设置好的联合仿真。

图3 裸Die电路原理图 + 基板Momentum联仿设置整体图 方法3:裸Die电路原理图 + 基板HFSS仿真 (Lumped端口去嵌)方法3步骤同方法2,不同之处在导出N端口S参数文件前将所有端口去嵌。

图4 基板HFSS仿真设置

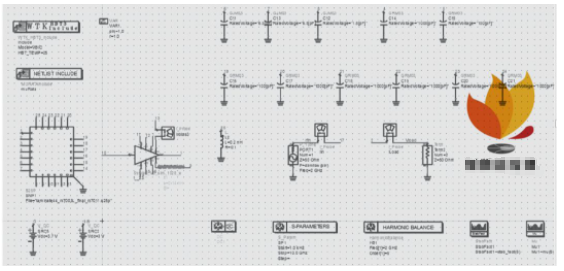

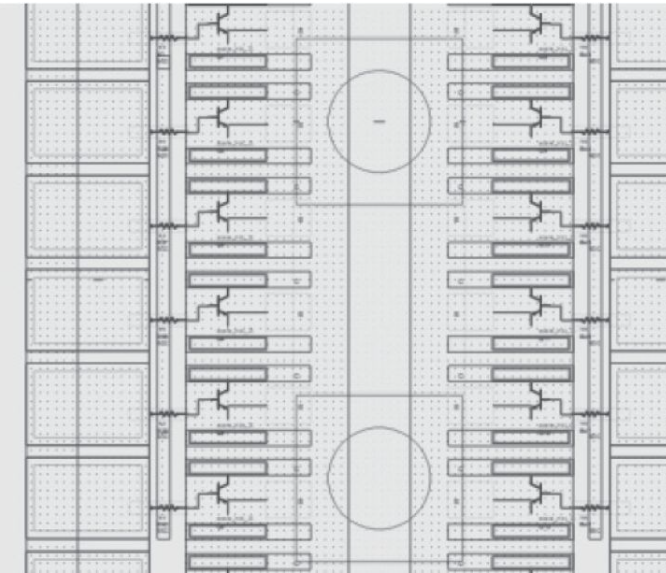

图5 裸Die电路原理图 + 基板HFSS联仿设置整体图 方法4:裸Die版图Momentum仿真 + 基板HFSS仿真 第1步:将设计好的PA裸Die版图(本例使用Cadence Virtuoso)导入到ADS layout里。 第2步:由于完整的PA裸Die版图EM仿真需要设置的端口非常多,仿真所需资源和内存也相应非常大,在目前中等配置的仿真硬件系统需要非常长的运行时间,甚至无法运行。方法4通常需要简化PA裸Die版图。鉴于高频寄生主要影响PA的输出级,方法4中PA Die版图只保留输出级和焊盘(PAD),并把所有有源器件和电阻去掉。然后类似于方法1中的第1步对简化版图进行ADS端口设置,每个连接三极管的地方需要设置3个PORT分别对应各极。如图6所示。 第3步:类似于方法1中的第2步,在ADS里创建Symbol并选择Symbol类型为Layout look-like,运行Momentum Microwave EM 仿真。仿真完毕会自动更新Symbol。 第4步:按方法2中第1-2步得到PA基板的HFSS仿真S参数文件。 第5步:在ADS原理图里,将本方法第1-3步所仿真好的PA裸Die版图Symbol与HFSS仿真所得到的基板S参数文件钩挂起来。 第6步:运行第5步设置好的联合仿真。

图6 简化PA裸Die版图和ADS端口设置 方法5:裸Die版图Momentum仿真 + 基板Momentum仿真 第1步:同方法4中的第1-3步,对PA裸Die版图进行Momentum仿真,得到PA裸Die版图仿真EMModel。 第2步:同方法1中的第1-2步,对PA基板版图进行Momentum仿真,得到PA基板版图仿真emModel。 第3步:在ADS原理图里,将本方法第1步所仿真好的PA裸Die版图EM Model与缺失的有源、无源器件以及本方法第2步所仿真好的PA基板版图emModel钩挂起来,局部如图7所示。 第4步:运行第3步设置好的联合仿真。

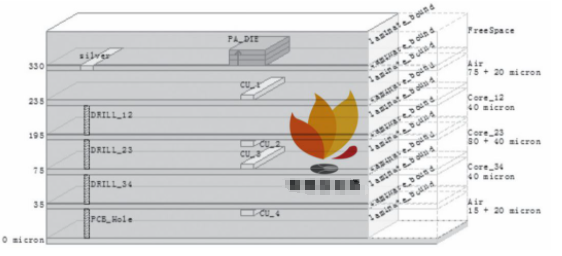

图7 PA裸Die版图emModel 钩挂有源、无源器件(局部) 方法6:裸Die版图 + 基板ADS嵌套技术 (Nested Technology)仿真ADS嵌套技术(Nested Technology)仿真方法详见ADS Help。本例的仿真版图嵌套设置和所创建的嵌套衬底文件如图8所示。

(a) ADS嵌套技术仿真端口设置

(b) 基板嵌套裸Die EM衬底设置 图8 本例的仿真版图嵌套设置和所创建的嵌套技术衬底文件 本例采用上述各种基板联合仿真方法对自主研制的PA芯片(PA#L03)进行仿真,其相应建模复杂度及仿真时间对比总结如表2所示(仿真系统配置:双核 3.2GHz CPU、16GB 内存、64位机; 仿真软件版本:ADS 2014、HFSS 15.0)。 表2 各种基板联合仿真方法的建模复杂度及仿真时间对比

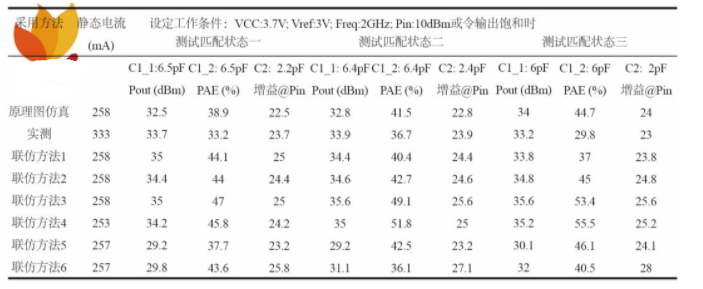

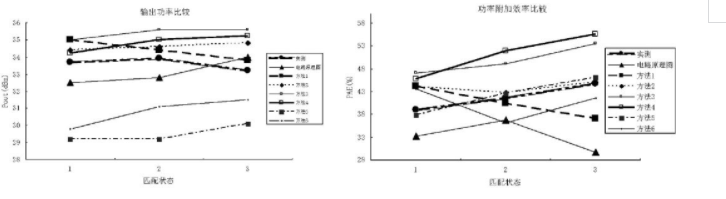

3 各种基板联合仿真的结果、电路原理图ADS仿真结果和实测结果对比 本例的PA#L0 3 芯片研制生产后进行了调试测试。上述各种基板联合仿真的结果、电路原理图ADS仿真结果和实测结果对比如表3所示(C1_1,C1_2,C2分别代表第1段匹配第1、2个电容和第2段匹配电容; Pout是输出功率; Pin是输入功率; PAE是功率附加效率)。图9对表3中的数据作了更直观的比较。

表3 各种基板联合仿真方法的仿真结果、电路原理图ADS仿真结果和实测结果对比

图9 表3数据的直观比较 4 结论 本文以自主研制的射频功率放大器芯片为例,从仿真器的算法理论、联合仿真的具体建模方法、建模复杂度、仿真时间、对比实测结果等几个方面对几种常用的基板联合仿真方法进行了比较探讨,尝试归纳总结出对实际射频功率放大器芯片工程设计可能有帮助的以下几点仿真经验(针对当前所使用软件版本): (1)电路原理图ADS仿真结果与实测结果已经比较接近,但为了提高仿真准确度,建议尽量进行基板EM联合仿真。 (2)采用HFSS设置Lumped端口仿真基板,不去嵌(方法2)比去嵌(方法3)的仿真结果更接近实测结果。 (3)采用裸Die电路原理图+基板EM仿真的方法(方法1,2)比电路原理图ADS仿真结果更接近实测结果:静态电流相差约22%; 输出功率相差约0.8~1.6dB; 效率相差约11%~33%。从准确角度上看,方法1和方法2相差不大;但利用HFSS的方法2比利用Momentum的方法1仿真时间要少很多,这从FEM和MoM的算法原理上是可以理解的。 (4)采用裸Die版图EM仿真+基板HFSS仿真的方法(方法4)在输出功率和增益的仿真上比方法1,2更接近实测结果,但耗时较长,且对效率的仿真不够准确。 (5)采用裸Die版图EM仿真+基板Momentum仿真的方法(方法5)并不准确且耗时长,不推荐采用。 (6)采用ADS 嵌套技术(方法6)并不准确且耗时长,也不推荐采用。 (责任编辑:admin) |