|

随着模数转换器(ADC)设计和架构不断改进,使用更小几何形状的工艺节点,一类新的GHz ADC产品开始出现。ADC能够以GHz及以上的速率直接进行RF采样,没有交错伪影,为通信系统、仪器仪表和雷达应用的直接RF数字化系统提供了新的解决方案。以前,这些解决方案需要多级滤波、频率合成器和混频器将输入信号转换为参考频率,然后由ADC以100s的MSPS转换速率进行数字化。现在,直接RF采样可以通过最先进的宽带ADC技术实现。请记住,速度虽然重要,但并不是设计中要考虑的唯一性能因素。应同等考虑动态范围和频谱噪声。我们将在以后的文章中探讨这些性能维度。 不久前,唯一能够以GSPS(每秒千兆采样)速度运行的单片ADC架构是具有1位或<>位分辨率的闪存转换器。它们耗电大,由于闪存架构的几何尺寸和功耗限制权衡,通常无法提供超过 <> 位的有效位数 (ENOB)。能够对高于<> GHz的更高动态范围模拟输入信号进行采样的唯一方法是将多个高速ADC内核与采样时钟交错,采样时钟与每个内核交错相位,具有精确的精度或占空比。模拟输入需要被分割和混频到每个ADC,这为新的信号噪声进入信号链并降低输入功率提供了机会。虽然这种方法可以为某些应用提供足够的结果,但设计很复杂,并且在输出频域中会产生令人讨厌的、不需要的交错伪影,需要对它们进行数字滤波。 快,还是半快? 交错“杂散”可以在快速傅里叶变换(FFT)的频率响应中看到,其中每个内部交错ADC内核的输入失调、增益、带宽和采样时序并不完全匹配。这给系统工程师带来了额外的规划复杂性,他们需要预先确定交错伪影的频率,并在数字后处理中避免或消除它们。由于每个ADC内核都是分立的,因此在生产中的系统生命周期内,这些性能参数之间可能存在很大的制造不匹配差异。这些失配会导致输入信号周期性不平衡,交错式ADC的输出端会出现杂散频率。 专有的ADC技术现在可以利用先进的架构和算法,防止双通道和四通道交错ADC中出现的问题。现在,无需在半速下使用两个交错式ADC,并增加伪影,现在可以在单个ADC中全速实现性能,而无需交错杂散。工厂调整算法和片内校准可确保每个ADC按照预期的高性能标准运行,而不是暴露于多个分立交错内核的失配差异。 当在其他频谱纯FFT中观察到杂散频率时,这会降低载波信号相对于其他噪声的可用无杂散动态范围(SFDR)。为了改善GSPS ADC的SFDR,新的架构和算法现在正在出现,而不仅仅是使用交错内核。这消除了系统工程师的负担,即必须识别和消除不需要的交错杂散的专用ADC后处理例程。

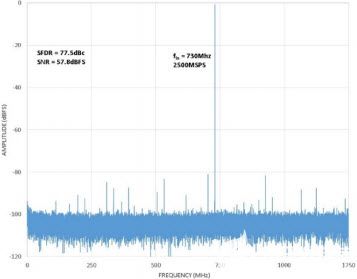

图1.宽带2.5 GSPS ADC的FFT显示高性能SFDR,没有交错伪像,而交错伪像在高速ADC中历来存在问题 简化路由 具有 10、12 或 14 位分辨率的千兆采样转换器会快速生成大量输出数据。对于30.1 GSPS、2位ADC,使用低压差分摆幅(LVDS)数据可能需要5个并行通道的12 Gbps数据。 每个ADC处理30个差分LVDS对可能很难在系统布局上布线和保持匹配长度。使用JESD204B(专为转换器接口设计的高速串行/反序列化(SERDES)标准)可以仅通过<>个或<>个差分通道发送等效数据。 JESD204B提供了一种在更少的数据线上高速输出数据的方法,而没有许多高速LVDS通道的时序板复杂性。由于通过JESD204B发送的数据基于嵌入式时钟和控制字符进行成帧,因此较低计数串行通道的路由比LVDS更能容忍时序偏差,如图2所示。这样就无需花费大量时间来调整系统 PCB 每个 I/O 上的输出时序。此外,JESD204B还提供辅助数据的信息“控制位”,可以附加到每个模拟样品中,以帮助表征下游处理。通过这种方式,可以为每个样本标记触发时间戳和超量程条件,以便后端FPGA可以进一步了解数据对齐及其有效性。

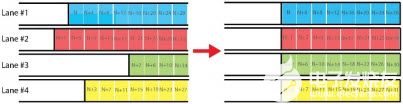

图2.JESD204B成帧协议允许数据通道之间和PCB布线内出现明显的时序偏差。FPGA 可以使用内部缓冲器延迟重新对齐数据和样本。 超量程检测 自适应增益算法对于能够调整模拟输入信号的幅度非常重要,因为饱和ADC输入基本上会使系统在破译信号的能力方面失明。理想情况下,增益自适应反馈环路应尽可能快。无论高速ADC输出是基于LVDS还是使用JESD204B,该数字输出增加的延迟通常都太长,无法等待以接收饱和数据、检测问题并对条件做出反应。 此问题的一个解决方案是在ADC内核本身内使用可变电平比较,并在发生超量程情况时直接发送即时输出标志。这种技术绕过了较长的后端输出级的延迟,从而缩短了放大器的反馈时间,从而实现更快的自适应增益周期。除了这种“快速超量程检测”输出外,还可以使用JESD204B接口在超量程样本后附加警报位,以便下游系统处理对数据做出适当的决策。 调优、筛选和抽取 — 如何处理所有数据 宽带ADC可以提供宽带采样的优势,但也可以提供比某些应用所需的更多的数据。对于那些需要高采样速率但不需要观察大频谱的系统,数字下变频(DDC)允许使用子采样和滤波策略来抽取GSPS ADC输出的数据量。然后,下游处理观察到频谱的较小部分。 虽然DDC通常在信号链中的ADC之后实现,这不仅会消耗FPGA中的更多资源,而且还需要在ADC和FPGA之间传输全带宽。DDC滤波可以在ADC内完成,而不是在FPGA中传输和处理采样数据,以仅查看总带宽的1/8或1/16。 当与合成数控振荡器(NCO)结合使用时,转换器DDC滤波器在频段中的精确位置可以通过精确的分辨率进行调整。这允许较低的输出速率,并且无需在FPGA上移动和处理大量不需要的数据。当有两个DDC可用时,每个DDC都有一个独特的NCO,它们可以交替地跨频谱进行步进以扫描预期信号,而不会损失可见性。这可能是某些雷达应用中的典型用途。

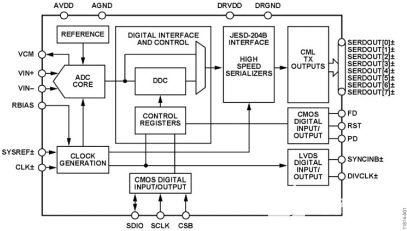

图3.9625位、2.5 GSPS ADC AD12-2.5的框图 ADI公司的AD9625-2.5 12位、2.5 GSPS ADC在宽带宽范围内提供优于–75 dBC SFDR性能,噪声频谱密度为150 dBFS/Hz。 ADI专有技术可实现这种性能,而不会出现采样速率高于1.5 GSPS的GHz ADC通常可以看到的交错伪像。带有宽带调谐器的可选双抽取下变频滤波器路径使系统设计人员能够仅观察 1/8 或 1/16 的全频谱带宽,每个带宽都具有独立的 10 位 NCO 放置分辨率。AD9625使用多达204个通道的JESD204B输出接口,从而减轻了LVDS对典型的匹配走线布线具有挑战性布局的需求。此外,设计人员还可以利用JESD<>B的优势,如低引脚数输出、谐波帧时钟、每个样本的控制位信息和确定性延迟。 总之,GHz ADC产品和系统的趋势部分是由更小的几何形状的工艺节点推动的,这些节点在未来十年内只会缩小尺寸。这将产生对更多能够直接RF转换的ADC的需求,从而简化架构并将设计时间控制在合理的范围内。正是这种速度、简化设计以及动态范围和低噪声等其他性能因素的结合,将把先进的宽带ADC技术推向一个新的水平,甚至更高。 审核编辑:郭婷 (责任编辑:admin) |