|

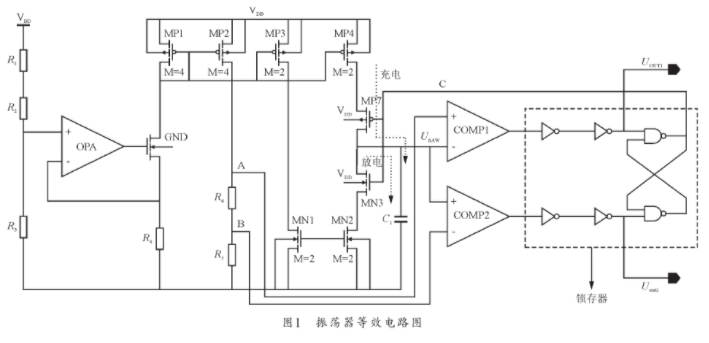

振荡器作为现代电子系统的重要组成部分,被广泛应用于时钟同步电路、无线通信收发器中的频率综合器、光通信中的时钟恢复电路(CRC,clock recovery circuit),以及多相位采样电路中。振荡器按实现电路元件分为RC振荡器、LC振荡器和石英晶体振荡器。 设计集成芯片内部的振荡电路的关键在于产生振荡信号频率的稳定性,它要求芯片不随工艺、温度、电源电压的变化而变化。本文采用内部正反馈的迟滞比较器设计了一种高稳定性宽电压范围的振荡器。该振荡器可以广泛使用在D类音频放大器中。 1 电路设计与原理分析 1.1 振荡器系统电路结构及原理 振荡器采用恒流源充放电技术,即利用恒定电流源提供的灌电流和拉电流分别埘电容进行充电和放电。振荡器的等效电路如图1所示。

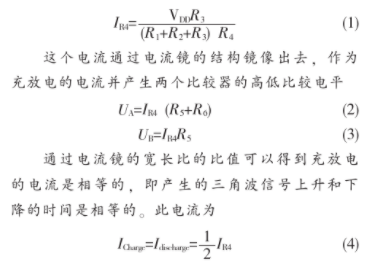

当振荡器工作时,通过OPA的钳位可以得到R4上端电压等于R3上的端电压,并由此产生一个恒定电流

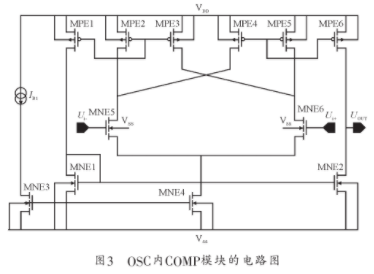

分析充放电的过程,假设使能开启使OSC工作,运放和比较器很快进入工作状态,比较的高低电平很快建立起来,输入至比较器。此时,电容上没有电荷,电压为零,与A和B比较,两个比较器分别输出高电平和低电平。 通过锁存器的工作使C为低电平,开启MP7给电容充电。当USAW大于B电平时,比较器COMP2翻转输出高电平,由于锁存器低电平触发,所以C维持低电半继续给电容充电,直到USAW的电平达到A点电平时,COMP1比较器输出低电平,触发C信号翻转输出高电平,电容开始放电,USAW的电平马上低于A点电平,比较器COMP1恢复输出高电平,如此循环往复的工作。所以USAW的输出正常工作之后是介于电平A和P之间的。 根据前面的公式推导,可以推出其周期公式。这里可以分两部分来分析 由于运放的输出电阻ROUT及电容C1很大,所以在输出端产生了一个低频的主极点。 该主极点为 1.3 比较器COMP 根据电路分析得,比较器COMP1为一级运放,采用了高速比较器结构,如图3所示。同时此结构也可以对电路的等效跨导增强,提高比较器的增益。

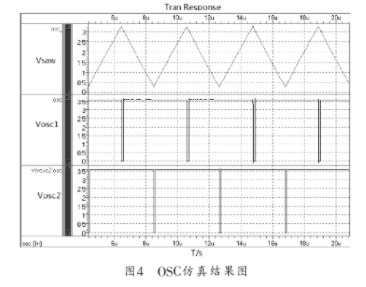

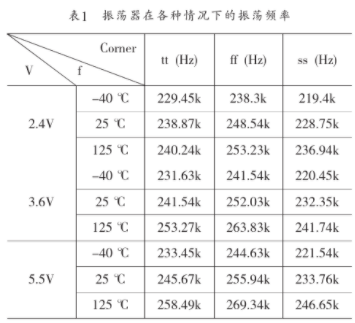

2 电路的仿真结果与分析 图4为振荡器仿真结果,表1为在不同电源电压及温度下振荡频率值。由表1可以得出该振荡器的频率受电源电压的影响比较小,随着温度上升则频率增大,不同的process corner下频率也不同。但是其波动范围都在电源管理芯片以及音频放大器芯片应用范围之内。

3 结束语 本文采用具有内部正反馈的迟滞比较器的结构,设计了一种基于CMOS工艺的高性能高稳定性的振荡器。该振荡器对电压、温度、工艺偏差具有较强的容忍度。经过仿真验证结果表明,该振荡器完全适用于D类音频放大器,DC/DC等芯片中。 责任编辑:gt (责任编辑:admin) |