|

ADC架构_Flash 比较器做1位ADC

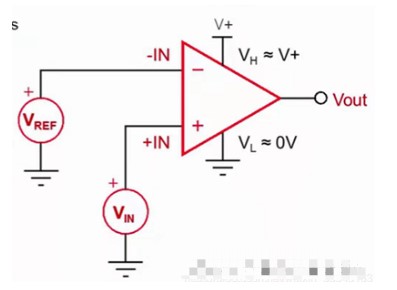

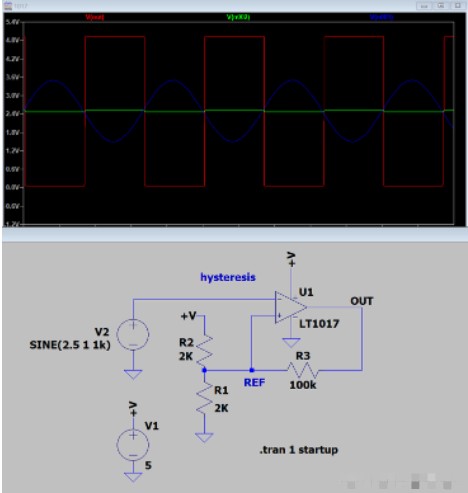

Vin > Vref Vout = High(1) Vin < Vref Vout = Low(0) 比较器是组建集成ADC的内部基本而又关键的模块;在比较器应用在ADC中一般要求很高的分辨率,也就是很小的差分输入信号,这就要求比较器的增益要非常的大,很小的差分输入信号会容易使比较器输出震荡,这就需要给比较器加入少量正反馈来做迟滞,滞回的电路如下图所示,通过调整反馈电阻R3的值就可以控制滞回电压的大小了,一般比较内部已经做了滞回,滞回的电压一般只有1~2mV,这个滞回的电压大小是不能超过比较器的分辨率的,所以不能为了抗干扰就用较大的滞回电压。

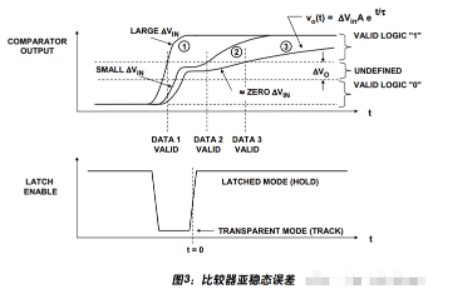

比较器的亚稳态问题 亚稳态问题如图3所示。其中展示了三种差分输入电压条件:(1) 大差分输入电压; (2)小差分输入电压; (3) 零差分输入电压。

对于小的差分电压输入时,亚稳态存在时间较长,如果读取数据在logic 0和logic 1之间读取数据时,数据很可能时错误的。解决这个问题可以提高增益(A),增加锁存的增益带宽以减小再生时间常数(τ),并为比较器输出达到有效逻辑电平给出充足的时间(t)。这个亚稳态对ADC的影响体现在误码率上,也叫做:闪码,飞码,跳码。 参考资料:ADC的MT-020 仿真没有看到这个亚稳态问题。

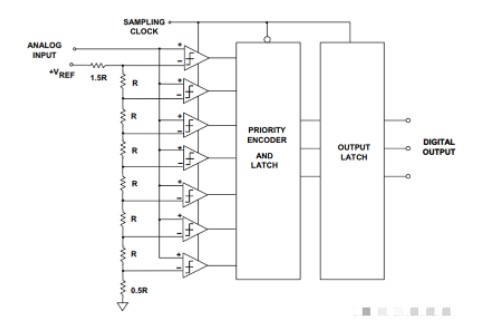

Flash并行转换器 Flash ADC的输入为一个并行比较的结构,下图为一个3位的Flash ADC,需要2N个电阻,2^N-1个比较器。 优点:输入输出的时延只是比较器,优先编码器(74HC148),锁存器的器件传输时延,所以从输入到输出的转换速度比较的快。 缺点:可以看出3位ADC已经用了7个比较器了,如果时8位ADC,就要用255个比较器,这个在工艺上是比较复杂,而且这么多的高速比较器同时工作,功耗也非常大,所以直接用2^N-1个比较器实现N位ADC不实际。

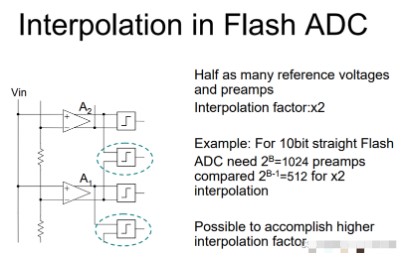

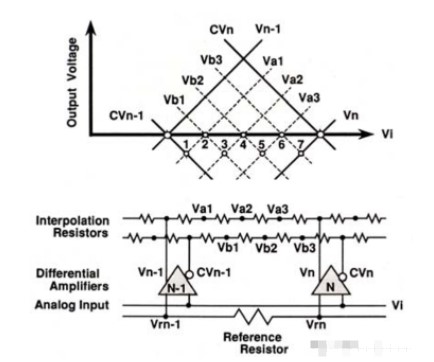

减少比较器数量的方法 利用差分输出的比较器,选择差分的两个输出端,这样就把2个采样点变成了3个,比较器的数量就减少了一半。

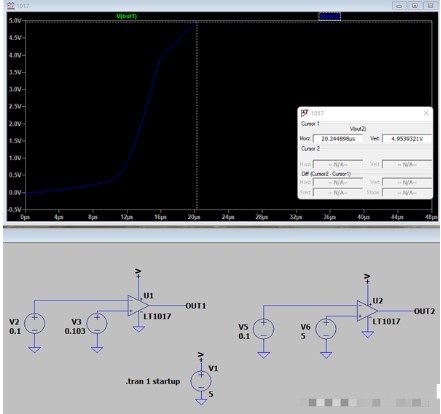

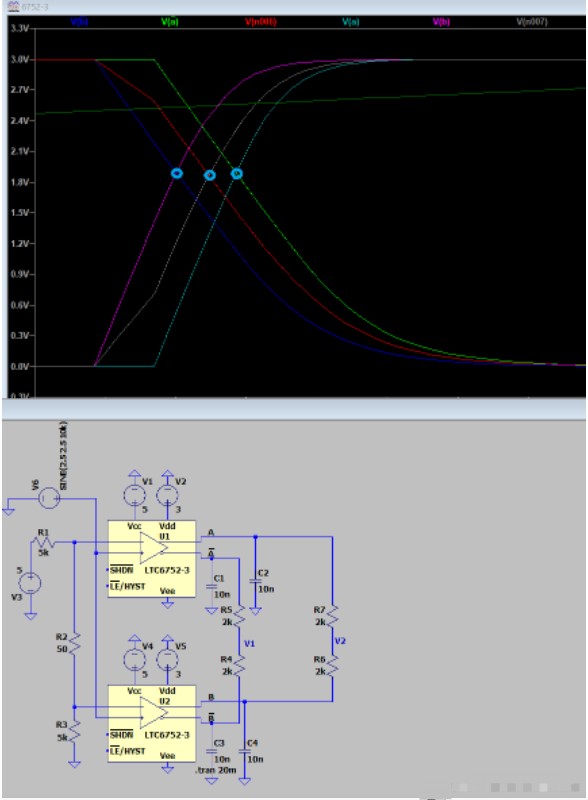

下面仿真可以看出两个差分输出的比较器实现了3个决策点的输出,实现了在两个采样点中间插值。

下图中把输出再用电阻分压,可以是比较器的数量进一步的减少。

|