|

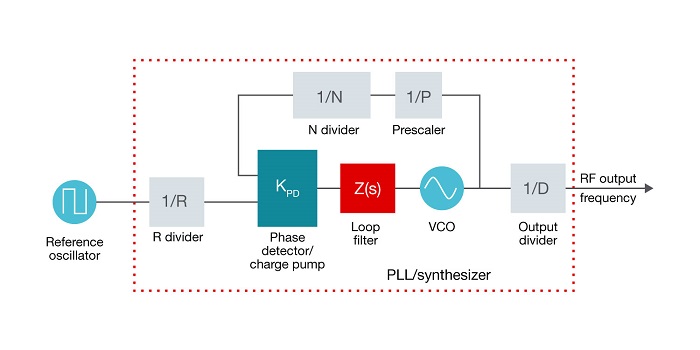

作者:Liam Keese,德州仪器公司时钟和计时产品应用经理。 为空间应用创建锁相环 (PLL) 合成器需要多个单独的组件和分立集成电路 (IC),它们占用大量体积并增加了大量质量。典型的 PLL 设计可能包括一个分立的压控振荡器 (VCO)、一个合成器,通常还有一个额外的预分频器/分频器或一个输出乘法器以适应更高的频率。在某些情况下,甚至使用离散的鉴相器/电荷泵来最小化系统噪声。 凭借大量关键组件,尺寸和复杂性可能会给工程师开发更小、更轻的系统并发射到太空带来设计挑战也就不足为奇了。 这与工程师在第一代移动设备中实施射频 (RF) 和微波组件时所面临的挑战类似。依靠当时可用的 IC,这些手持设备需要大量的分立元件——导致设备昂贵、体积大,电池寿命极短。 虽然手机和卫星系统中的合成器有很大不同的要求,但它们在保持性能同时减少质量/体积方面面临相同的挑战。那么,我们是如何从砖块大小的纯语音电话转变为我们今天使用的时尚、便携、支持数据的智能手机,卫星系统设计人员如何简化他们的 PLL 设计?通过将射频和合成器组件集成到单片射频 IC 中。 集成对于今天的设计师来说并不是一个陌生的概念,也不局限于空间或手机设计。通信卫星采用范围广泛的射频和微波频率。卫星对地和星间通信系统日益复杂,需要新的架构概念。 现有的分立合成器解决方案包含多个组件,包括多个 VCO、PLL 分频器、电荷泵和支持电路,可占用 8 × 10 英寸的占位面积。通过更高的集成度,可以将相同的功能安装到 1 × 1 英寸的印刷电路板区域中。 重要的是尽量减少整体功耗,以避免任何额外热量散发的问题。使用集成低压差稳压器提供内部电源,无需更多外部抗辐射组件。 集成还有助于提高可靠性。与使用分立 VCO 模块相比,使用集成多核 VCO 实现宽带合成器是一种直观且更具成本效益的方法,可最大限度地减小系统尺寸。溶液表面积越小,杂散重离子撞击关键部件并破坏正常运行的机会就越低。图 1 提供了适用于完全或部分集成到单片 RF IC 中的 PLL/合成器功能块的视觉参考。

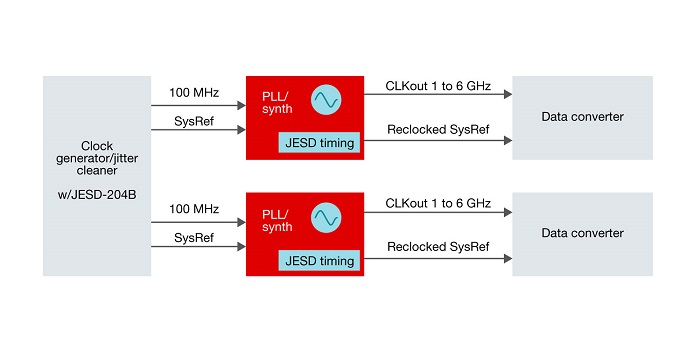

图 1:用于完全或部分集成到单片 RF IC 中的 RF PLL/合成器功能块 然而,对于现代卫星 PLL 合成器设计,集成只是创建真正“空间就绪”设计的开始。工程师还应考虑一些性能指标,以进一步减少星载 PLL 的解决方案尺寸和质量,包括: 辐射免疫 宽频率范围 低噪音性能 时钟同步 辐射免疫 太空中的硬真空并不是最受人欢迎的环境,尤其是对于电子元件而言。鉴于大量的辐射,设备必须准备好在太空中生存并按预期运行。辐射容限要求取决于任务剖面。太空就绪设备是一种抗辐射 IC,能够承受高总电离剂量 (TID),提供足以在地球同步轨道上安全运行多年的保护水平。 无论您是计划发射卫星成像有效载荷还是完成星际旅行,都必须考虑 TID。TID 量化了任务期间随时间累积的带电粒子辐射量,并且必须针对每个半导体晶圆或晶圆批次进行测试。虽然典型的半导体工艺变化可能对器件的电气性能几乎没有影响,但不同条件下的辐射硬度性能可能存在显着波动。 太空就绪设备也在光束下进行单粒子效应 (SEE) 测试。验证对各种 SEE 故障机制的免疫力可通过重离子轰击宇宙射线引起的破坏性事件确保设备功能。高辐射环境中的太空任务将要求 SEE 抗扰度水平具有任务剖面可接受的平均故障间隔时间 (MTBF),而低地球轨道卫星可能具有可接受的 MTBF,该值略低一些。 在选择太空就绪设备时,重要的是选择一家具有为此类超高可靠性环境生产硬件的成熟传统的半导体制造商。业内人士了解这种情况的严重性,要求设备具有抗辐射能力,并来自合格制造商清单 V 类。对于为太空飞行而开发的半导体产品,晶圆批次通常会进行辐射性能表征以及辐射批次验收测试 (RLAT),其中对来自每个晶圆批次或晶圆的样品进行测试并符合一定水平的 TID,以便设备可以被认为是抗辐射和空间就绪的。 宽频率范围 通信卫星使用范围广泛的射频和微波频率,因此频率范围和灵活性也是任何 PLL/VCO 构建模块的关键参数。RF 时钟系统的范围可以从 100 MHz 到超过 X 波段 (>12 GHz)。在最好的情况下,您可以使用相同的宽带组件进行设计,无论是开发 12 至 18 GHz Ku 波段的固定波束成形卫星发射器系统、频率捷变射频通信接收器还是高性能 L 波段 GPS系统。多个应用程序中的组件重用还减少了对多个设备进行鉴定的需要,并有助于更好地管理飞行时间风险。 为了涵盖各种应用,RF 输出频率应该在很宽的频率范围内进行编程,并且建立的延迟时间非常短。与堆叠分立 VCO 模块相比,在设计集成解决方案时,实施多核 VCO 是一种更容易的技术。分频器可以帮助将范围扩展到较低的频率,还可以降低宽带噪声。 低噪音性能 通信系统——尤其是卫星中的通信系统——需要一个低抖动时钟源来对输入的模拟接收信号进行采样,构建任何发射机调制波形,并在各种子系统之间提供同步。时钟源中的任何相位噪声或抖动都会在模拟信号的采样值中引入噪声。时钟源中的过度抖动或集成相位噪声可能会限制可实现的信噪比和/或最大工作带宽。 高性能 PLL 的设计人员努力限制各种噪声源的影响。一种主要的噪声源是 PLL 噪声本底品质因数 (FOM),由于其平坦的频率响应与频率之间的关系,有时也称为平坦噪声。近端相位噪声或 1/f 噪声主要是 VCO 有源电路的一个因素。归一化 1/f 噪声和 FOM 的典型值分别优于 –120 dBc/Hz 和 –230 dBc/Hz。您通常可以在产品数据表中找到这两种噪声源的源数据。 PLL N 分频器还会以 20 logN 的速率添加噪声,因此一般来说,更高的鉴相器频率会产生更好的输出噪声。输出分压器 D 具有相反的效果;但是,它可以将输出噪声降低 20 logD,但需要权衡增加的复杂性和电流。这些噪声源以及环路带宽将决定 PLL 的噪声性能。 时钟同步 在星载应用中为多个数据转换器计时或创建波束成形阵列时,一个常见问题是如何保持同步。时钟源之间的偏斜或时序偏移和不确定的延迟会使维持高速稳健的通信链路变得困难。单片合成器可以轻松集成配置相位同步功能,以帮助在多通道系统中实现低偏移。确定性同步不需要在时钟路径之间相同,只要它是确定性和可重复的。及时向前或向后“步进”合成器输出允许您使用在上电时保持一致的设置来调整相对时钟偏差。 为高速数据转换器(例如 SYSREF)提供时钟的久经考验的技术支持符合联合电子设备工程委员会 JESD204B 标准,如图2 所示。目标是实现从输入到输出的确定性相位,并允许将时钟到时钟的偏移调整到小于 10 ps。延迟一致的事实意味着它可以在软件中进行纠正,或者允许支持生成或重复符合 JESD204B 标准的 SYSREF。

图 2:使用 JESD204B/C 的典型系统时钟图 准备起飞了吗? 如果您正在寻找启动空间就绪射频合成器项目或寻找如何在现有设计平台中节省空间,希望就在眼前。一些关键要求现在在开始时更容易检查,通过集成 RF IC 技术帮助您解决空间就绪设计的困难性能要求。 审核编辑:汤梓红 (责任编辑:admin) |