|

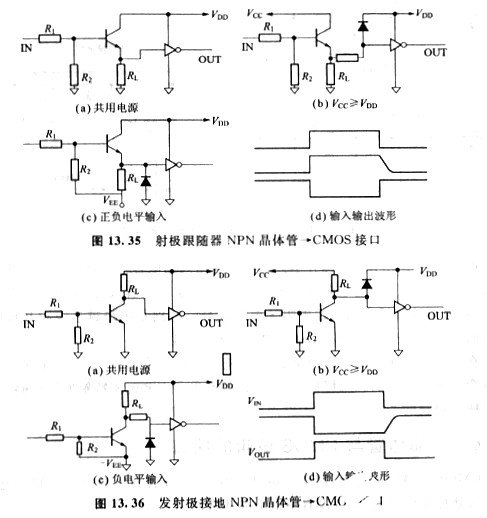

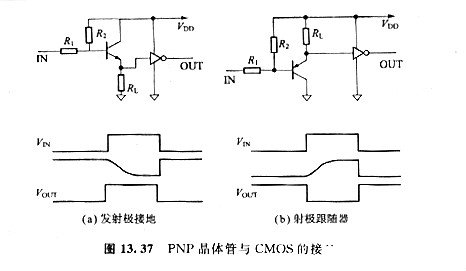

CMOS电路的最末级,通常是用显现器显现,或者介入继电器控制大电流,或者向远处传送信号等,很少没有不借助晶体管的。 但是,在与这个晶体管接口时的困难不测地多。例如,由于与晶体管的基极连接的电阻过于小,从CMOS引出过大电流;或者电阻过大,使晶体管无法驱动。 下面对各种场所与晶体管的接口作以说明。 (1)发射极接地NPN晶体管→CMOS:图l3.35(a)一(c)示出同~电源下,Vcc》VDD,Vcc (2)射极跟随器NPN晶体管→CMOS:与(1)的情况相反,在“L”电平常容易混入噪声,存在从“L”向“H”时容易产生延迟的缺陷。图13.36(a)一(c)示出接口例。 (3)发射极接地PNP晶体管→CMOS:如图13. 37(a)所示,在降落时有延迟,在“L”电平要留意噪声。 (4)射极跟随器PNP晶体管→CMOS:其例子示于图13. 37(b)。与(3)的情况相反,上升时产生延迟,“H”电平抗噪声才干弱。

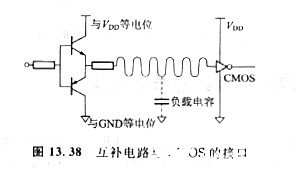

(5)互补电路→CMOS:在(1)~(4)的电路中,当晶体管个CMOS的布线变长时,在“H”或者“L”电平,噪声容易混入,由于布线电容而增大延迟时间。由于这些缺陷,所以对布线的长度有限制。这种情况下,运用图13.38所示的互补电路使阻抗降落,关于改善噪声和延迟时间有效果。

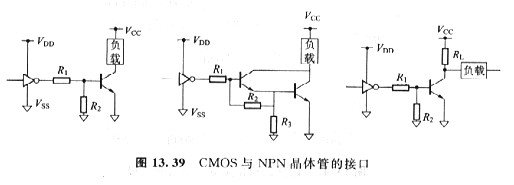

(6) CMOS→NPN晶体管:CM0S的输出端由于负载过重而招致电流缺乏,或者耐压缺乏的场所,需求这种接口。 由于经过CMOS的p沟FET流出的电流(IOH)变成晶体管的基极电流,所以能够驱动它的hfe的电流。进而在驱动大负载的场所,运用达林顿晶体管。 图13. 39示出NPN晶体管驱动电路的例子。

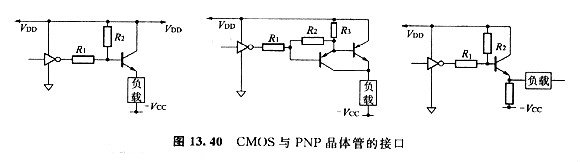

(7) CMOS→PNP晶体管:图13. 40示出电路例。

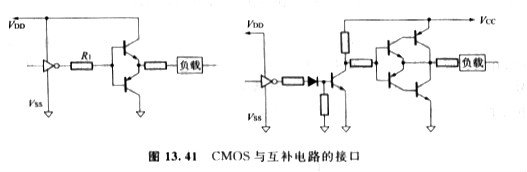

(8) CMOS→互补电路:将CMOS电路的信号向远方传送的场所,如前所述,为了抗噪声、防止布线电容惹起的延迟,应该采用互补电路。其接口例子示于图13. 41。

责任编辑:gt (责任编辑:admin) |